# CIRCUIT DESIGN

# know it all

- A 360 degree view from our best-selling authors

- Key facts, techniques, and applications fully detailed

- The ultimate hard-working desk reference; all the essential information, techniques, and tricks of the trade in one volume

Ashby • Baker • Ball • Crowe • Hayes-Gill • Hickman • Kester Mancini • Grout • Pease • Tooley • Williams • Wilson • Zeidman

# INCLUDES

FREE NEWNES ONLINE MEMBERSHIP

Circuit Design

#### The Newnes Know It All Series

#### PIC Microcontrollers: Know It All

Lucio Di Jasio, Tim Wilmshurst, Dogan Ibrahim, John Morton, Martin Bates, Jack Smith, D.W. Smith, and Chuck Hellebuyck ISBN: 978-0-7506-8615-0

#### Embedded Software: Know It All

Jean Labrosse, Jack Ganssle, Tammy Noergaard, Robert Oshana, Colin Walls, Keith Curtis, Jason Andrews, David J. Katz, Rick Gentile, Kamal Hyder, and Bob Perrin ISBN: 978-0-7506-8583-2

#### Embedded Hardware: Know It All

Jack Ganssle, Tammy Noergaard, Fred Eady, Lewin Edwards, David J. Katz, Rick Gentile, Ken Arnold, Kamal Hyder, and Bob Perrin ISBN: 978-0-7506-8584-9

#### Wireless Networking: Know It All

Praphul Chandra, Daniel M. Dobkin, Alan Bensky, Ron Olexa, David Lide, and Farid Dowla ISBN: 978-0-7506-8582-5

#### RF & Wireless Technologies: Know It All

Bruce Fette, Roberto Aiello, Praphul Chandra, Daniel Dobkin, Alan Bensky, Douglas Miron, David Lide, Farid Dowla, and Ron Olexa ISBN: 978-0-7506-8581-8

# Electrical Engineering: Know It All

Clive Maxfield, Alan Bensky, John Bird, W. Bolton, Izzat Darwazeh, Walt Kester, M. A. Laughton, Andrew Leven, Luis Moura, Ron Schmitt, Keith Sueker, Mike Tooley, DF Warne, Tim Williams ISBN: 978-1-85617-528-9

#### Audio Engineering: Know It All

Douglas Self, Richard Brice, Don Davis, Ben Duncan, John Linsley Hood, Morgan Jones, Eugene Patronis, Ian Sinclair, Andrew Singmin, John Watkinson ISBN: 978-1-85617-526-5

#### Circuit Design: Know It All

Darren Ashby, Bonnie Baker, Stuart Ball, John Crowe, Barrie Hayes-Gill, Ian Grout, Ian Hickman, Walt Kester, Ron Mancini, Robert A. Pease, Mike Tooley, Tim Williams, Peter Wilson, Bob Zeidman ISBN: 978-1-85617-527-2

#### Test and Measurement: Know It All

Jon Wilson, Stuart Ball, GMS de Silva, Tony Fischer-Cripps, Dogan Ibrahim, Kevin James, Walt Kester, M. A. Laughton, Chris Nadovich, Alex Porter, Edward Ramsden, Stephen Scheiber, Mike Tooley, D. F. Warne, Tim Williams ISBN: 978-1-85617-530-2

#### Mobile Wireless Security: Know It All

Praphul Chandra, Alan Bensky, Tony Bradley, Chris Hurley, Steve Rackley, John Rittinghouse, James Ransome, Timothy Stapko, George Stefanek, Frank Thornton, Chris Lanthem, Jon Wilson ISBN: 978-1-85617-529-6

For more information on these and other Newnes titles visit: www.newnespress.com

# Circuit Design

Darren Ashby Bonnie Baker Stuart Ball J. Crowe Barrie Hayes-Gill Ian Hickman Walt Kester Ron Mancini Ian Grout Robert A. Pease Mike Tooley Tim Williams Peter Wilson Bob Zeidman

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2008, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: permissions@elsevier.com. You may also complete your request online via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

Library of Congress Cataloging-in-Publication Data

Application submitted

# British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

ISBN: 978-1-85617-527-2

For information on all Newnes publications visit our Web site at www.elsevierdirect.com

Printed in the United States of America 08 09 10 10 9 8 7 6 5 4 3 2 1

Working together to grow libraries in developing countries www.elsevier.com | www.bookaid.org | www.sabre.org ELSEVIER BOOK AID International Sabre Foundation

# **Contents**

| About the Authors                                       | xv  |

|---------------------------------------------------------|-----|

| Chapter 1: The Fundamentals                             |     |

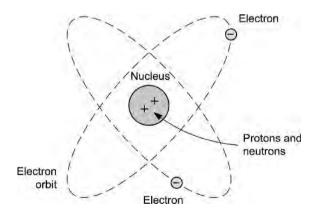

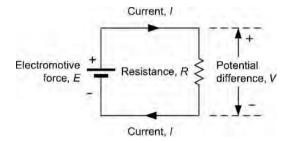

| 1.1 Electrical Fundamentals                             |     |

| 1.2 Passive Components                                  |     |

| 1.3 DC Circuits.                                        |     |

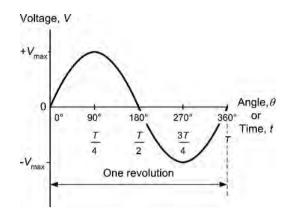

| 1.4 Alternating Voltage and Current                     |     |

| 1.5 Circuit Simulation                                  |     |

| 1.6 Intuitive Circuit Design                            |     |

| 1.7 Troubleshooting Basic                               |     |

| References                                              |     |

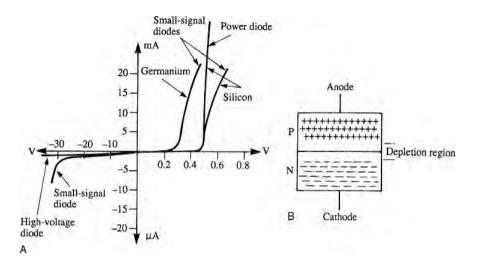

| Chapter 2: The Semiconductor Diode                      |     |

| References                                              |     |

|                                                         |     |

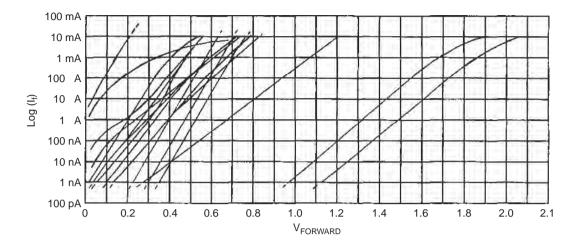

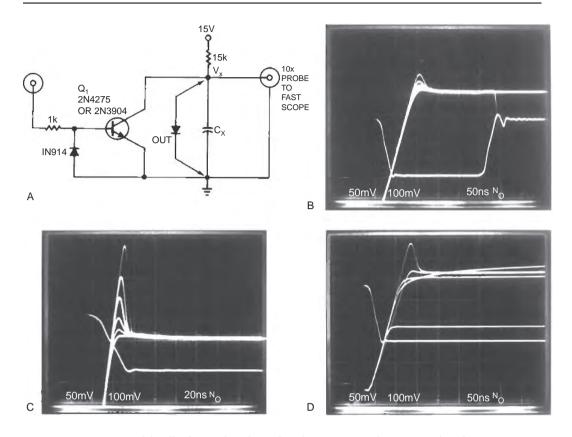

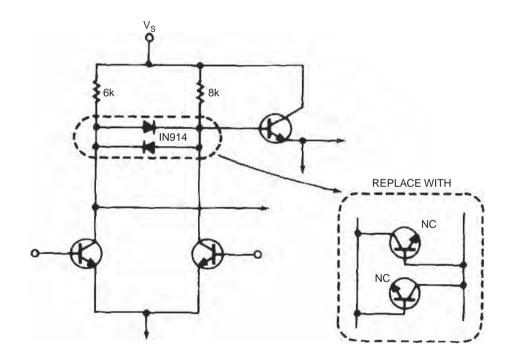

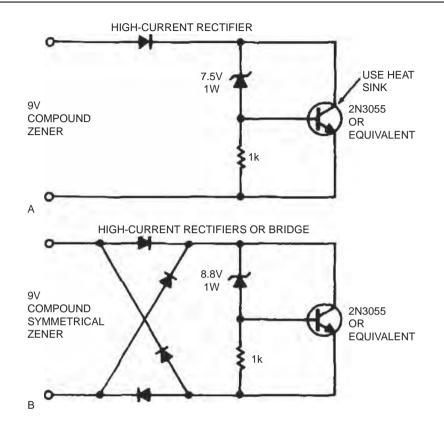

| Chapter 3: Understanding Diodes and Their Problems      | 217 |

| 3.1 Speed Demons                                        |     |

| 3.2 Turn 'em off—turn 'em on                            |     |

| 3.3 Other Strange Things that Diodes Can Do to You      |     |

| 3.4 Zener, Zener, Zener                                 |     |

| 3.5 Diodes that Glow in the Dark, Efficiently           |     |

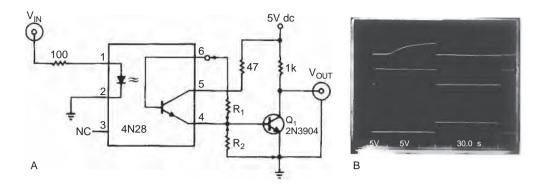

| 3.6 Optoisolators                                       |     |

| 3.7 Assault and Battery                                 |     |

| References                                              |     |

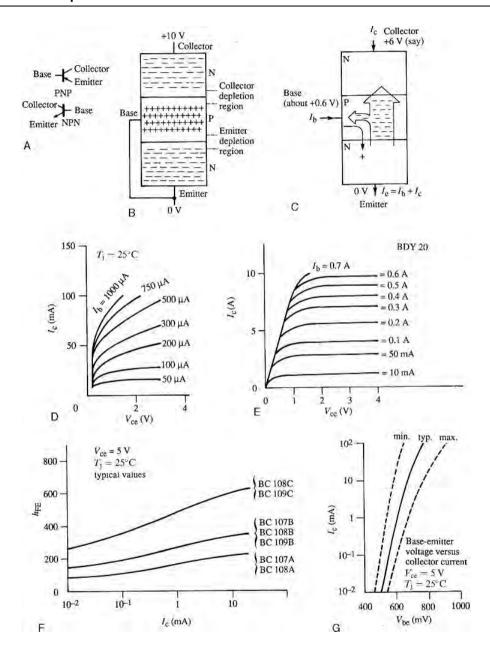

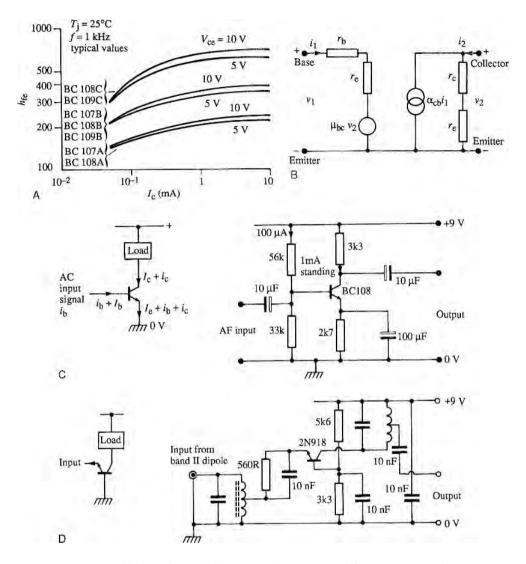

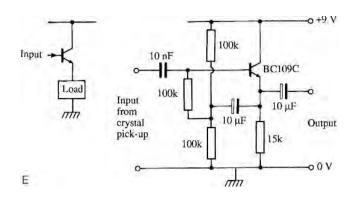

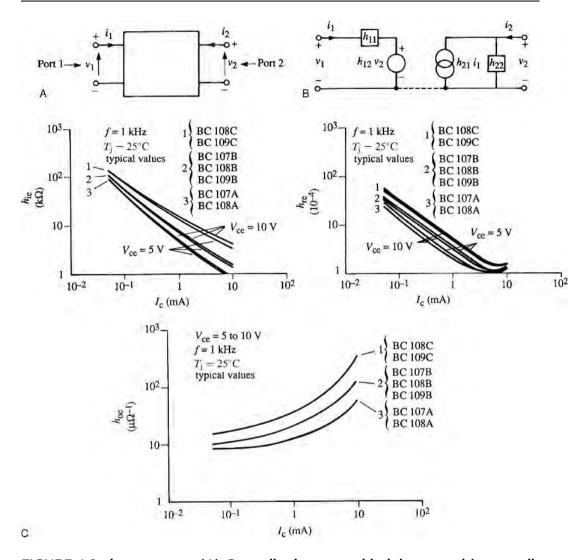

| Chapter 4: Bipolar Transistors                          | 235 |

| References                                              |     |

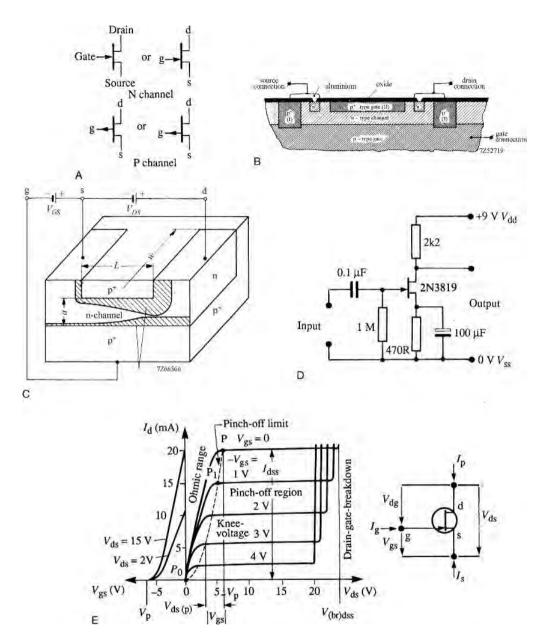

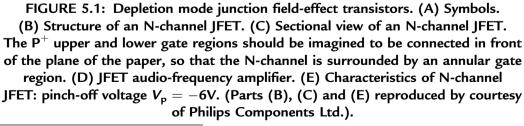

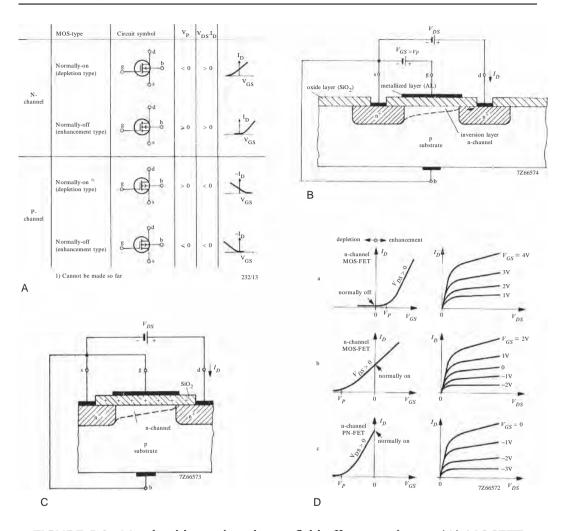

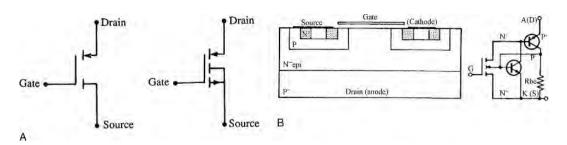

| Chapter 5: Field-Effect Transistors                     | 249 |

| References                                              |     |

|                                                         |     |

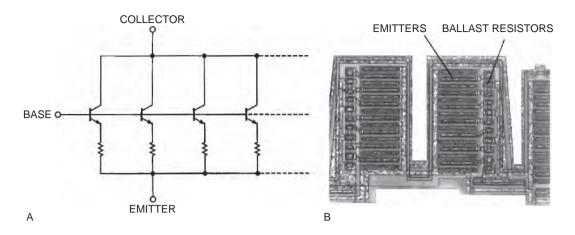

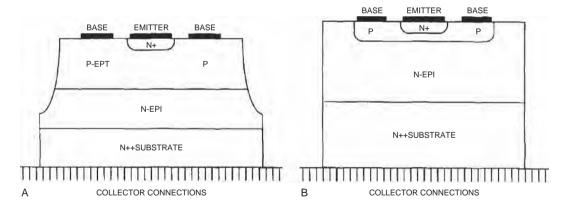

| Chapter 6: Identifying and Avoiding Transistor Problems | 255 |

| 6.1 More Beta—More Better?                              |     |

| 6.2 Field-Effect Transistors                            |     |

| 6.3          | Power Transistors may Hog Current        |     |

|--------------|------------------------------------------|-----|

| 6.4          | Apply the 5-Second Rule                  |     |

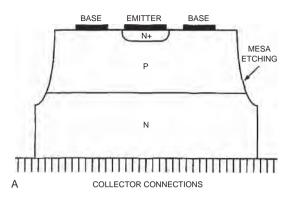

| 6.5          | Fabrication Structures make a Difference |     |

| 6.6          | Power-Circuit Design Requires Expertise  |     |

| 6.7          | MOSFETs Avoid Secondary Breakdown        |     |

| Refe         | erences                                  |     |

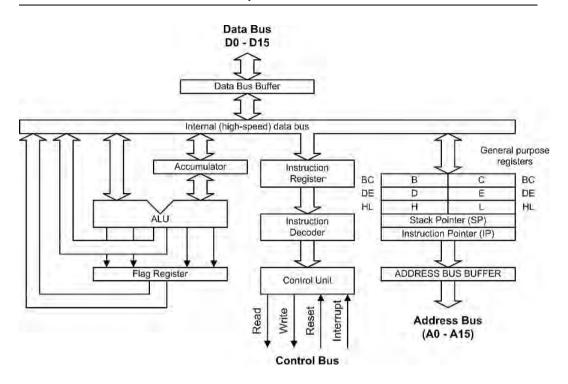

| Chab         | ter 7: Digital Circuit Fundamentals      | 271 |

| 7.1          | Digital Technology                       |     |

|              | prences                                  |     |

|              |                                          |     |

| -            | ter 8: Number Systems                    |     |

| 8.1          | Introduction                             |     |

| 8.2          | Decimal–Unsigned Binary Conversion       |     |

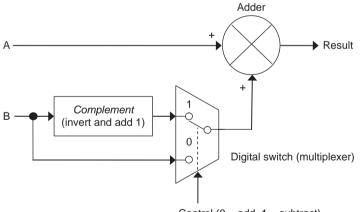

| 8.3          | Signed Binary Numbers                    |     |

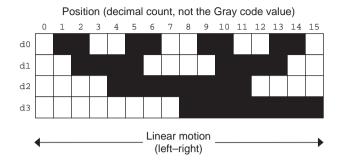

| 8.4          | Gray Code                                |     |

| 8.5          | Binary Coded Decimal                     |     |

| 8.6          | Octal-Binary Conversion                  |     |

| 8.7          | Hexadecimal-Binary Conversion            |     |

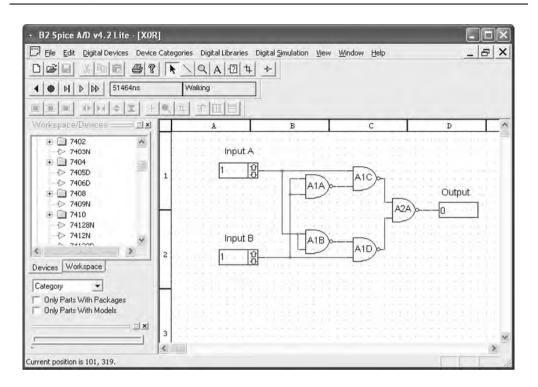

| Chap         | ter 9: Binary Data Manipulation          |     |

| 9.1          | Introduction                             |     |

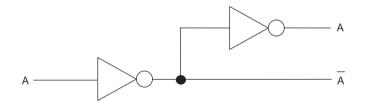

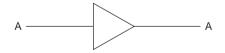

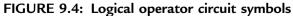

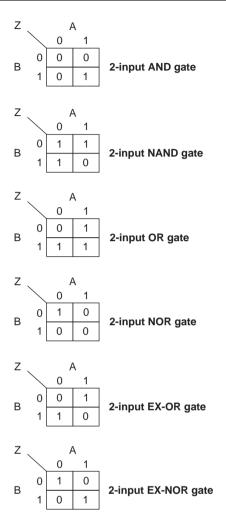

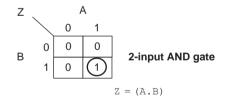

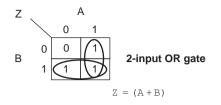

| 9.2          | Logical Operations                       |     |

| 9.3          | Boolean Algebra                          |     |

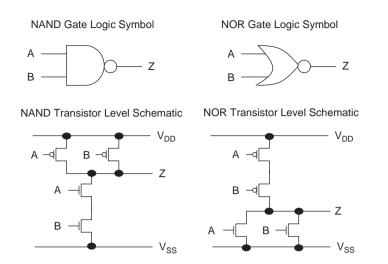

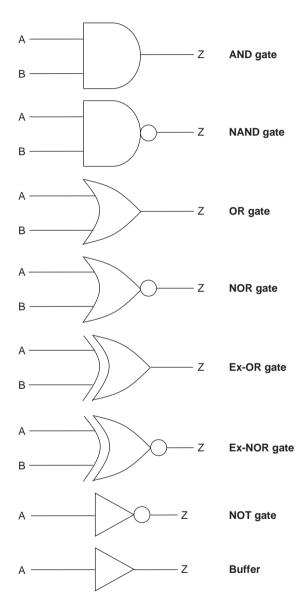

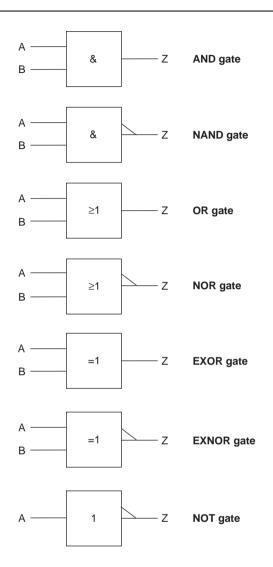

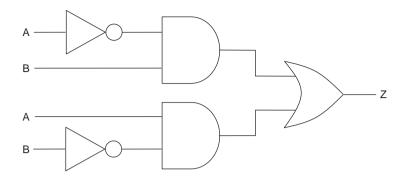

| 9.4          | Combinational Logic Gates                |     |

| 9.5          | Truth Tables                             |     |

| Refe         | erences                                  |     |

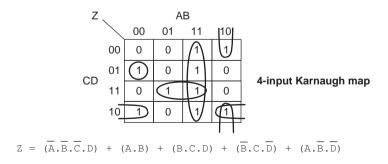

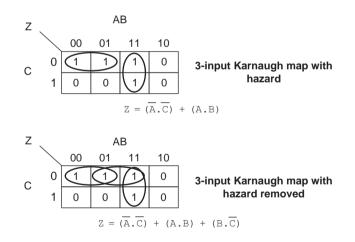

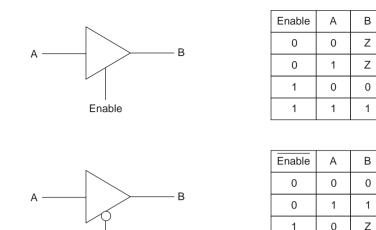

| Chat         | ter 10: Combinational Logic Design       |     |

| 10.1         |                                          |     |

| 10.2         |                                          |     |

| 10.3         | e e                                      |     |

| 10.4         |                                          |     |

| Refe         | erences                                  |     |

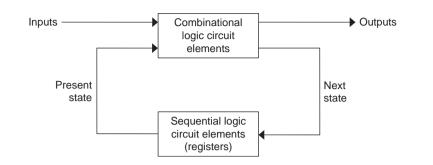

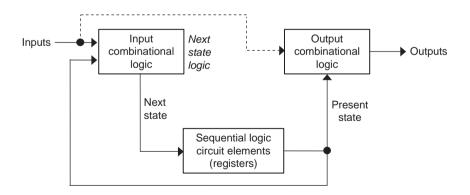

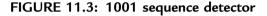

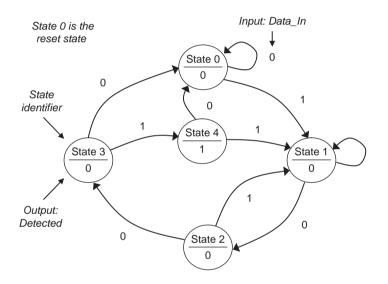

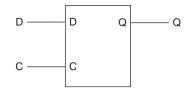

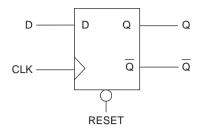

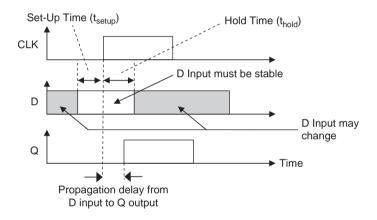

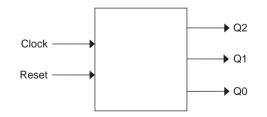

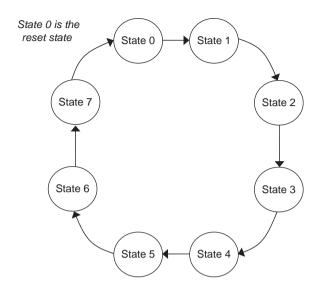

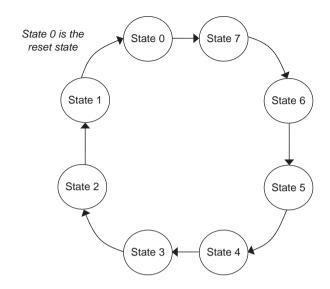

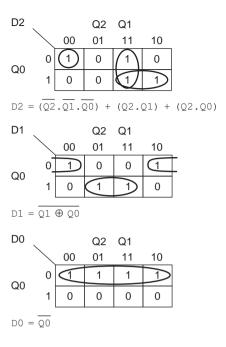

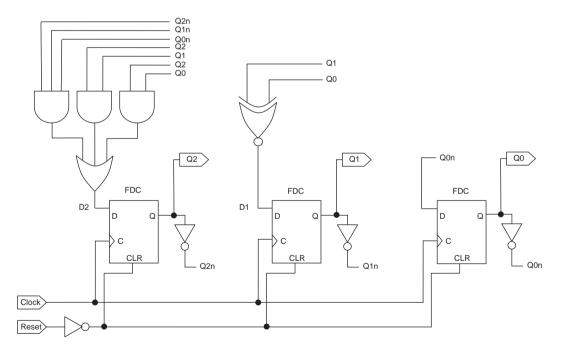

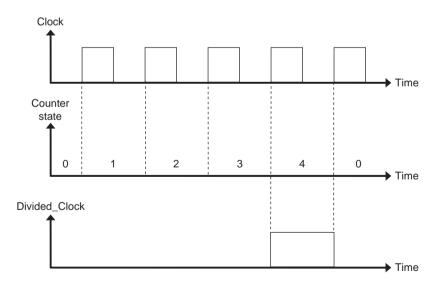

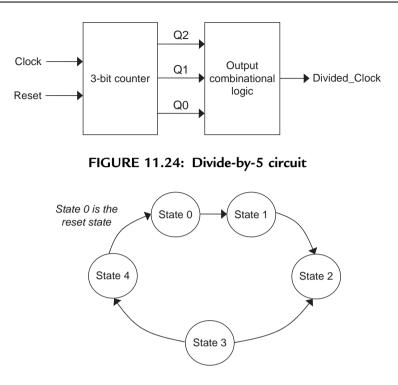

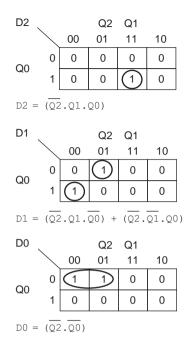

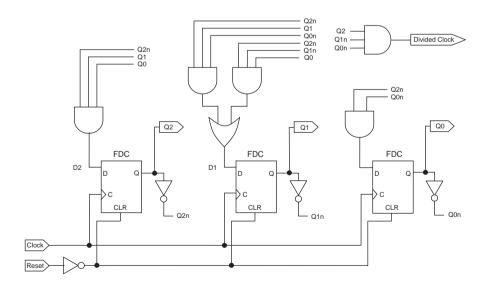

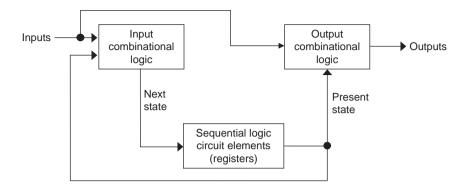

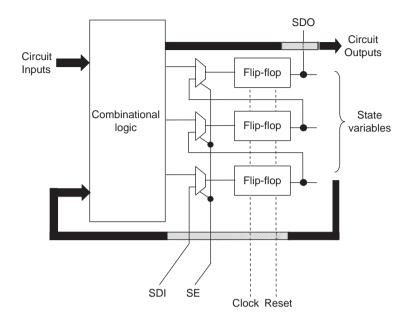

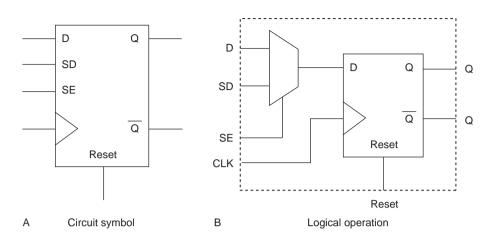

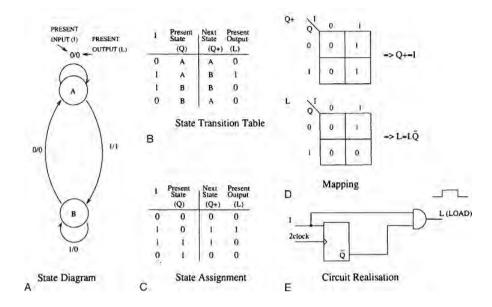

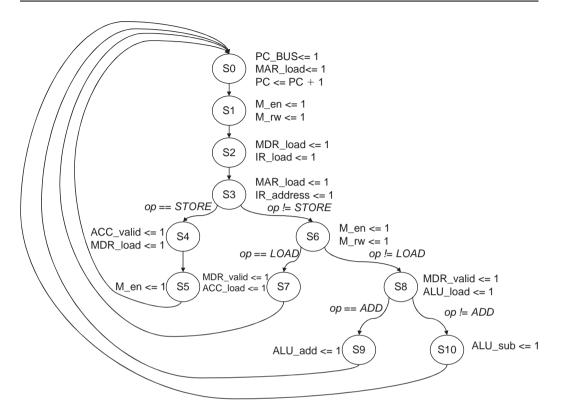

| Chan         | ter 11: Sequential Logic Design          | 2/2 |

| 11.1         |                                          |     |

|              |                                          |     |

| 11.2<br>11.3 |                                          |     |

|              |                                          |     |

| 11.4         | 8                                        |     |

| 11.5         |                                          |     |

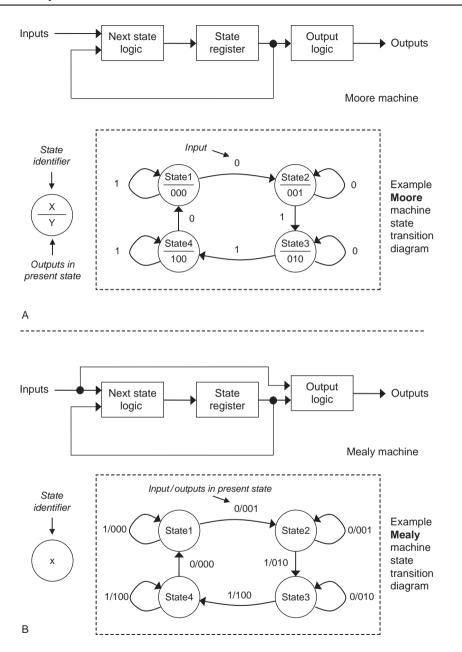

| 11.6         | Moore Versus Mealy State Machines        |     |

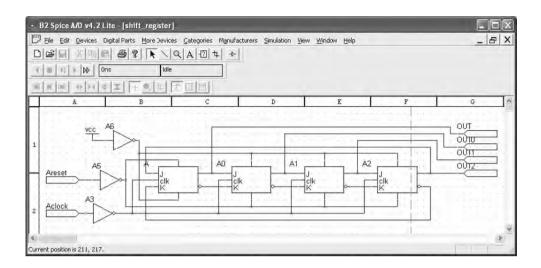

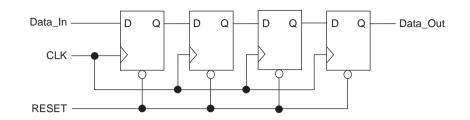

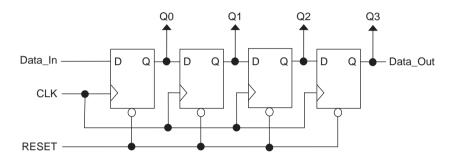

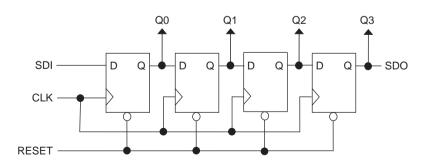

| 11.7           | Shift Registers                                                    | 377 |

|----------------|--------------------------------------------------------------------|-----|

| 11.8           | Digital Scan Path                                                  |     |

| Refere         | nces                                                               | 382 |

|                |                                                                    |     |

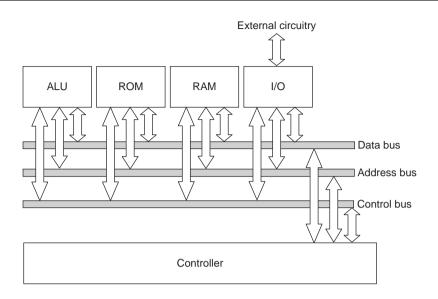

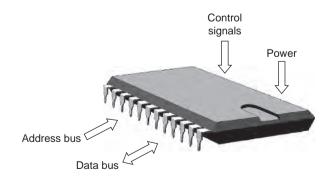

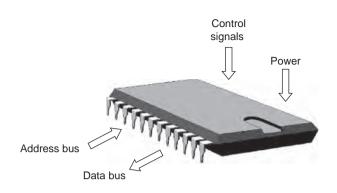

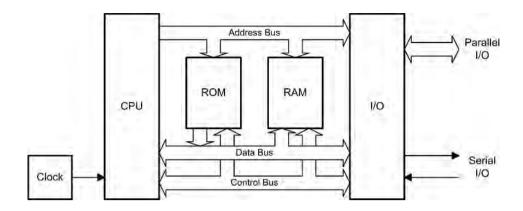

| Chapte         | r 12: Memory                                                       | 383 |

| 12.1           | Introduction                                                       |     |

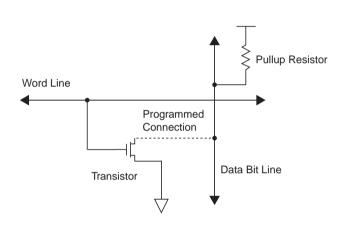

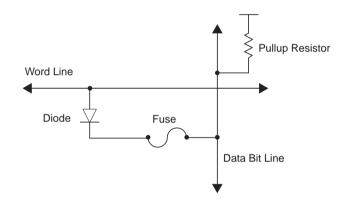

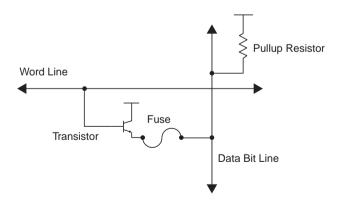

| 12.2           | Random Access Memory                                               | 385 |

| 12.3           | Read-only Memory                                                   | 386 |

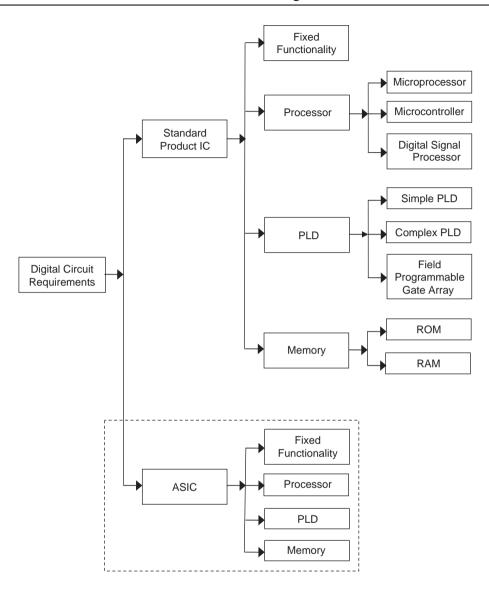

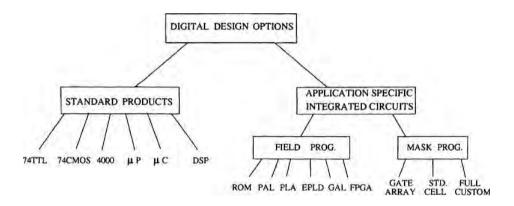

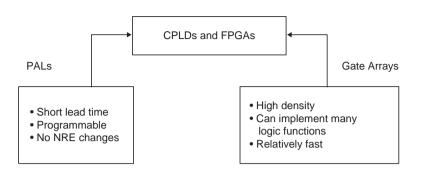

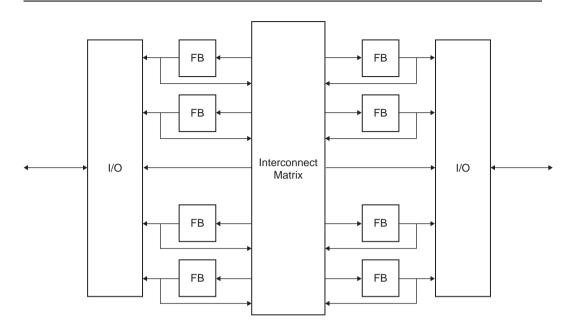

| Chapte         | r 13: Selecting a Design Route                                     | 389 |

| 13.1           | Introduction                                                       |     |

| 13.1           | Discrete Implementation                                            |     |

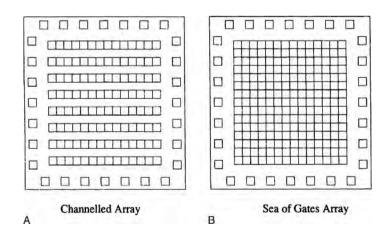

| 13.2           | Mask Programmable ASICs                                            |     |

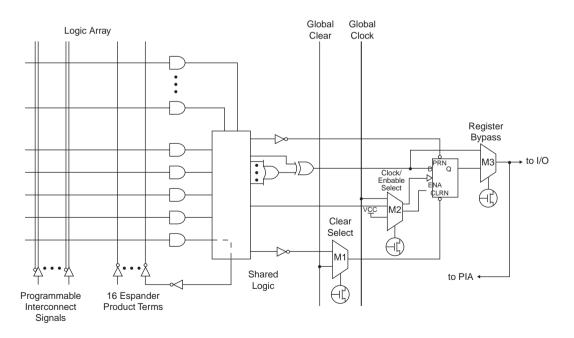

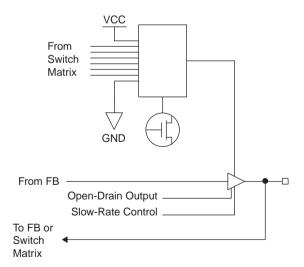

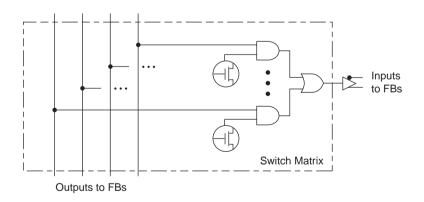

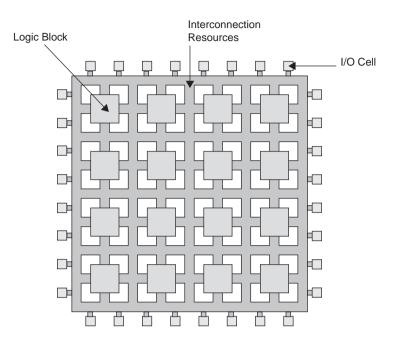

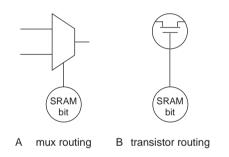

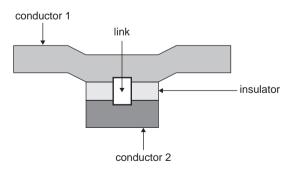

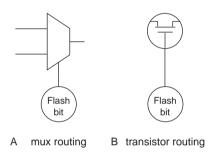

| 13.4           | Field-Programmable Logic                                           |     |

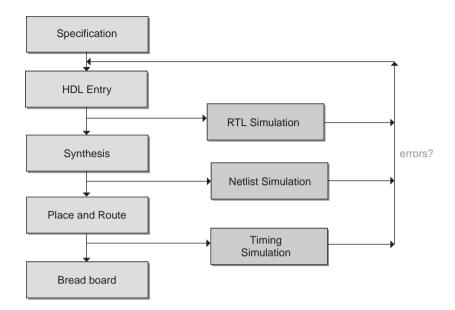

| 13.5           | VHDL                                                               |     |

| 13.6           | Choosing a Design Route                                            |     |

|                |                                                                    |     |

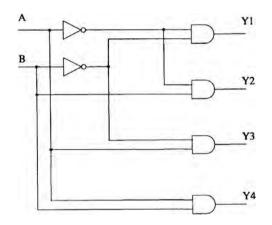

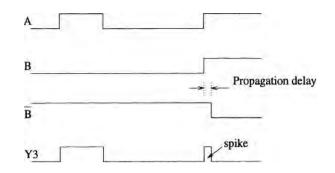

|                | r 14: Designing with Logic ICs                                     |     |

| 14.1           | Logic ICs                                                          | 441 |

| Chapte         | r 15: Interfacing                                                  | 455 |

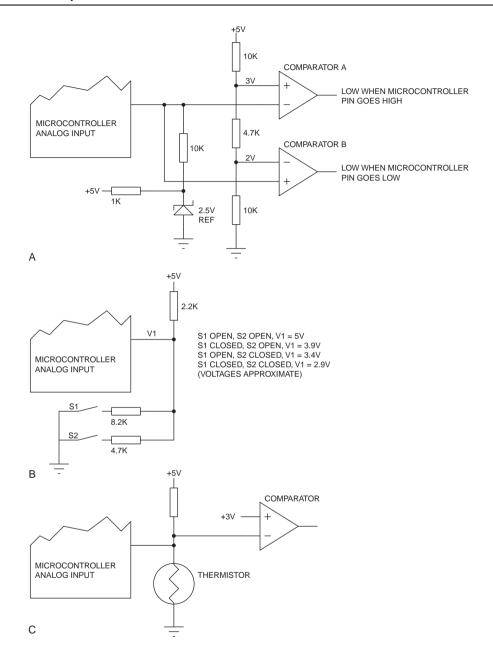

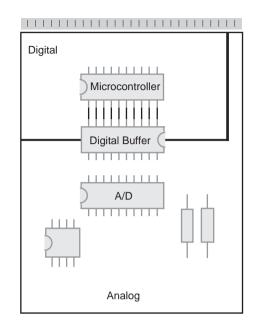

| 15.1           | Mixing Analog and Digital                                          |     |

| 15.2           | Generating Digital Levels from Analog Inputs                       |     |

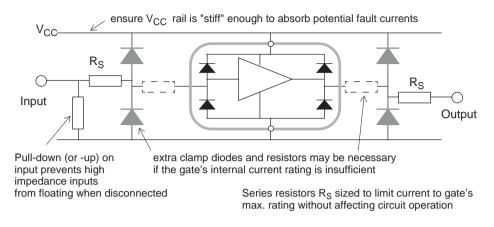

| 15.3           | Protection Against Externally Applied Overvoltages                 |     |

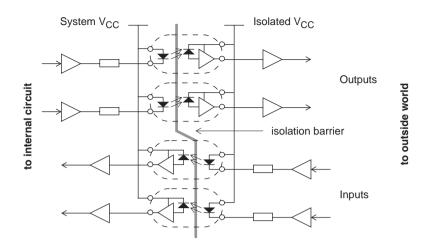

| 15.4           | Isolation                                                          |     |

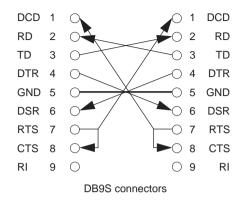

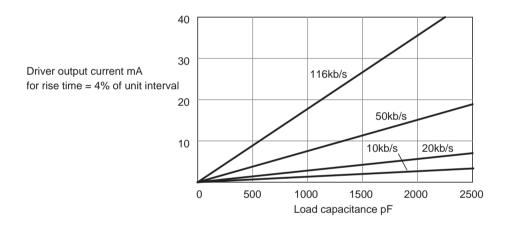

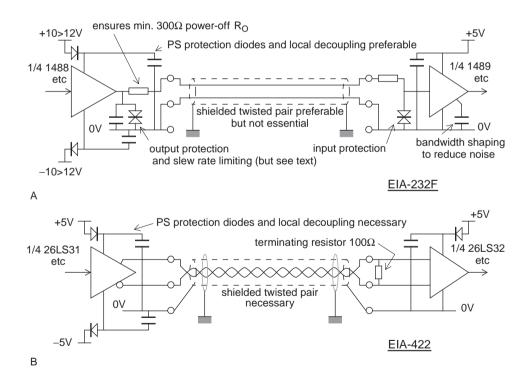

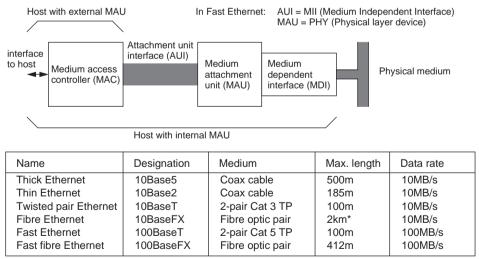

| 15.5           | Classic Data Interface Standards                                   |     |

| 15.6           | High-Performance Data Interface Standards                          |     |

| _              |                                                                    |     |

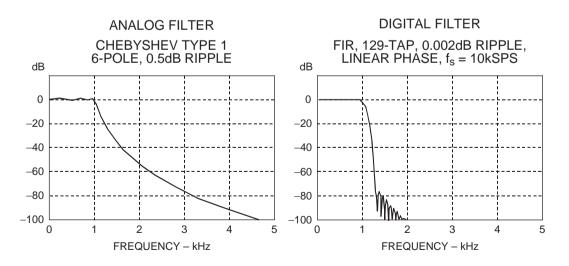

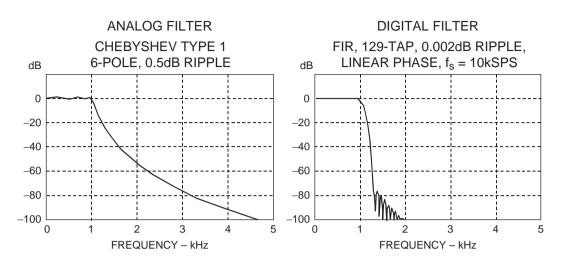

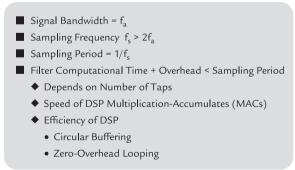

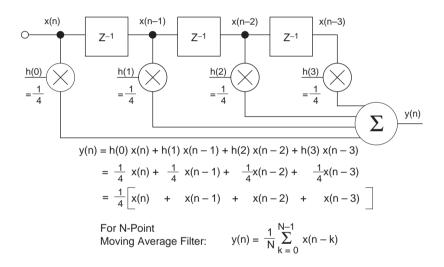

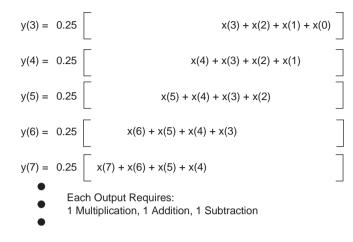

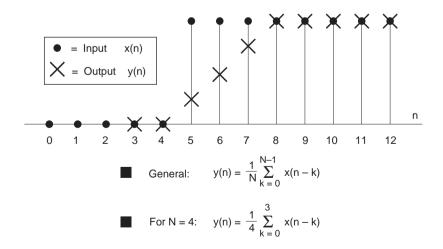

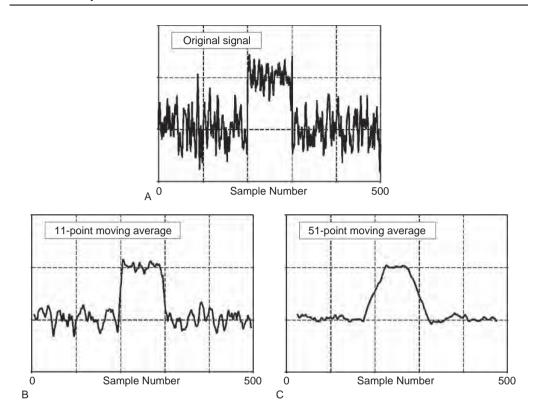

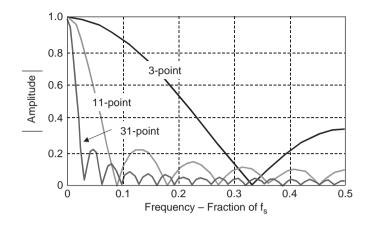

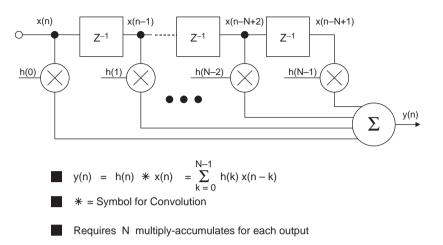

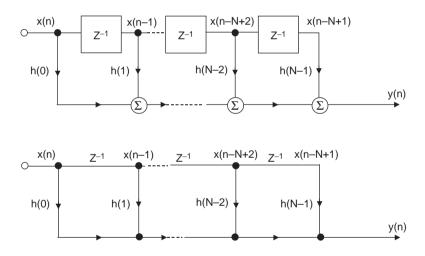

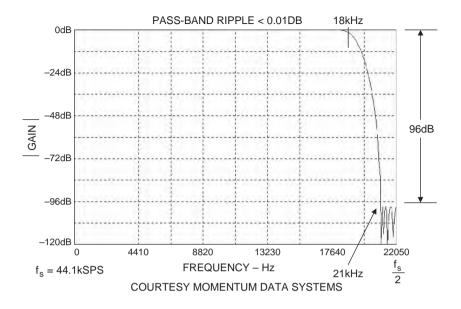

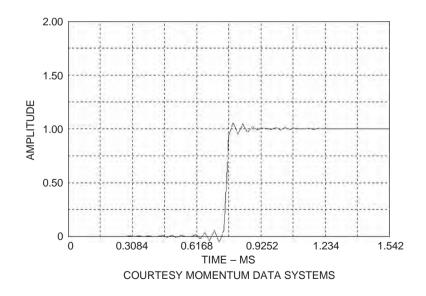

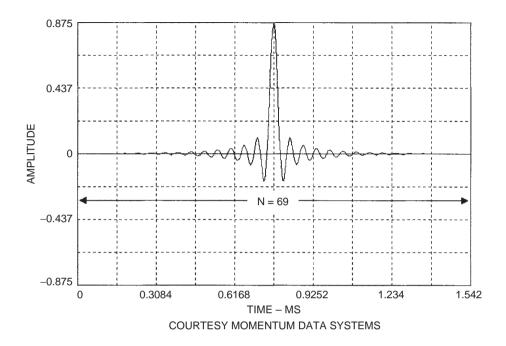

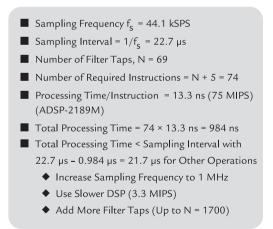

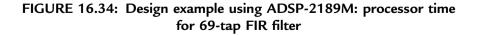

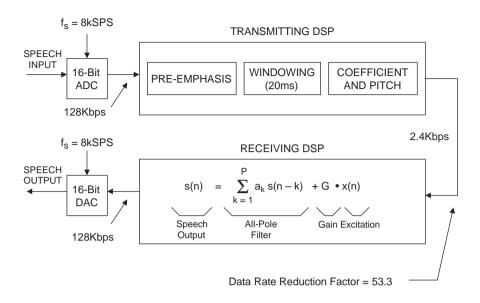

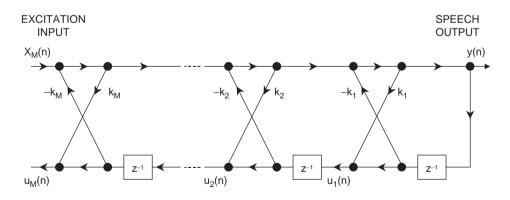

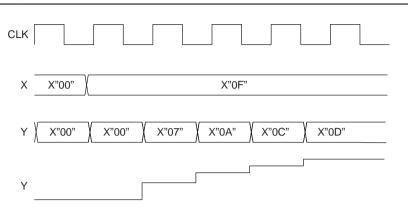

|                | r 16: DSP and Digital Filters                                      |     |

| 16.1           | Origins of Real-World Signals and Their Units of Measurement       |     |

| 16.2           | Reasons for Processing Real-World Signals                          |     |

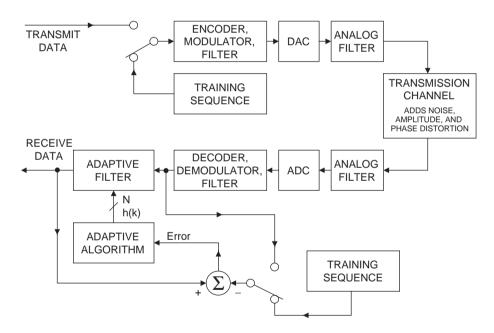

| 16.3           | Generation of Real-World Signals                                   |     |

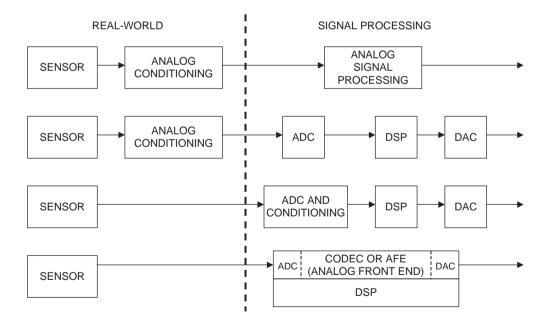

| 16.4           | Methods and Technologies Available for Processing Real-World Signa |     |

| 16.5           | Analog Versus Digital Signal Processing                            |     |

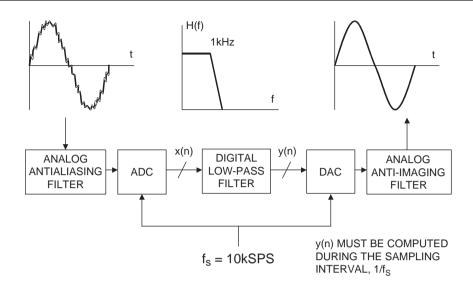

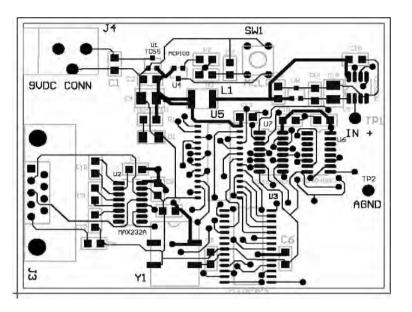

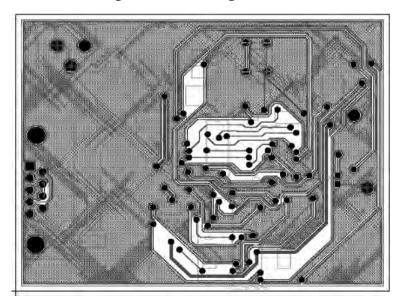

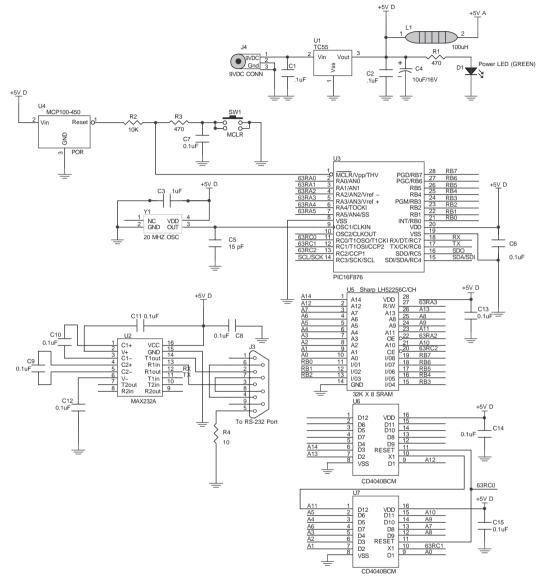

| 16.6           | A Practical Example                                                |     |

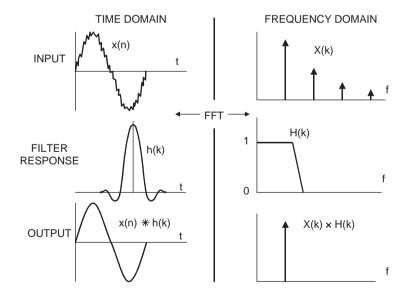

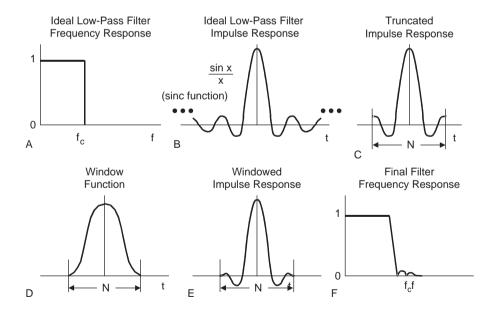

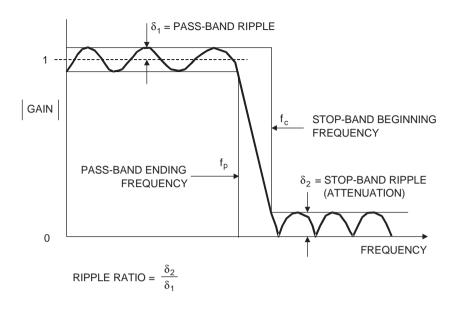

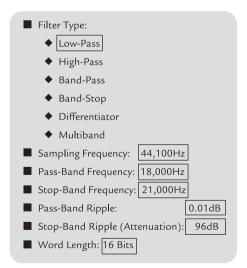

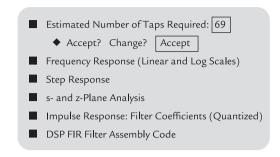

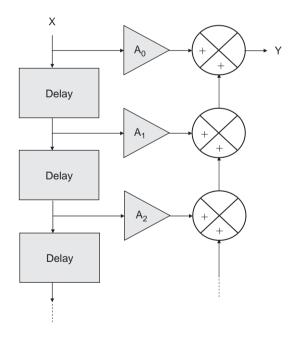

| 16.7           | Finite Impulse Response (FIR) Filters                              |     |

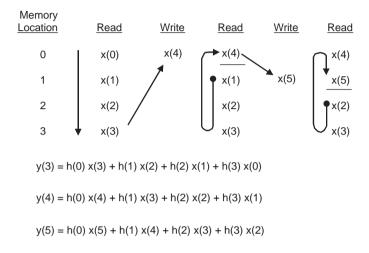

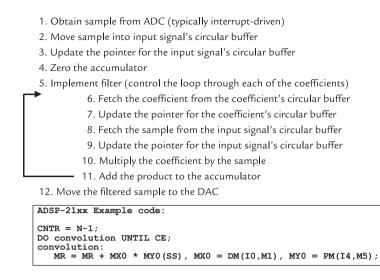

| 16.8           | FIR Filter Implementation In DSP Hardware Using Circular Buffering |     |

| 16.9           | Designing FIR Filters                                              |     |

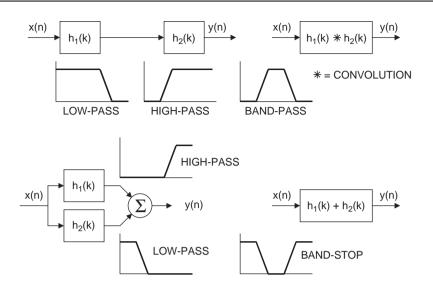

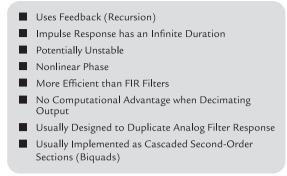

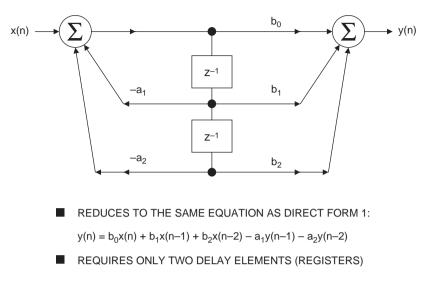

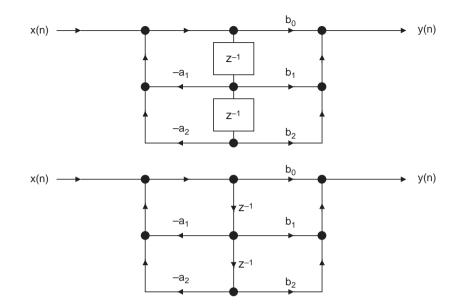

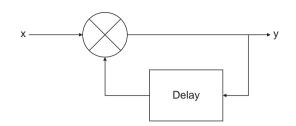

| 16.10          | Infinite Impulse Response (IIR) Filters                            |     |

| 16.11<br>16.12 | IIR Filter Design Techniques                                       |     |

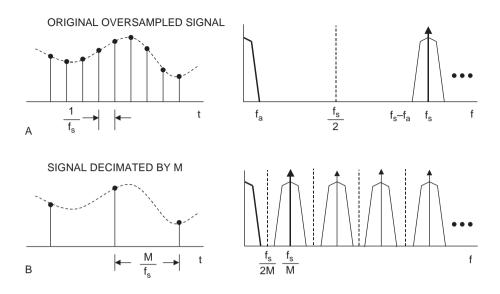

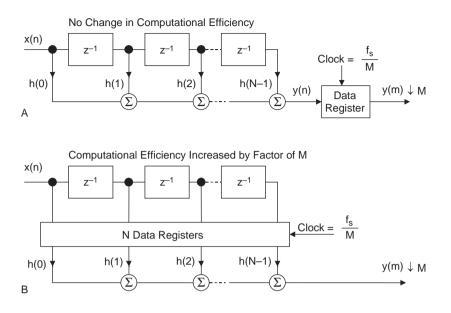

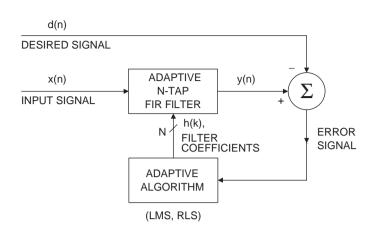

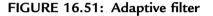

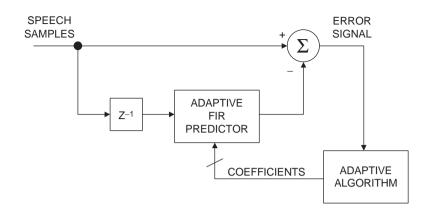

| 16.12          | Multirate Filters<br>Adaptive Filters                              |     |

|                | Adaptive Filters                                                   |     |

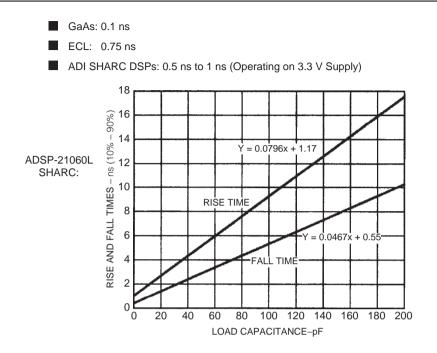

| Chapte | r 17: Dealing with High-Speed Logic                              | 525 |

|--------|------------------------------------------------------------------|-----|

| -      | nces on Dealing with High-Speed Logic                            |     |

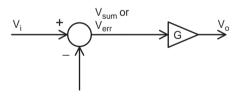

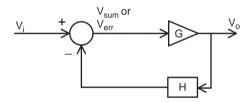

| Chante | r 18: Bridging the Gap between Analog and Digital                | 533 |

| 18.1   | Try to Measure Temperature Digitally                             |     |

| 18.1   | Road Blocks Abound                                               |     |

| 18.3   | The Ultimate Key to Analog Success                               |     |

| 18.4   | How Analog and Digital Design Differ                             |     |

| 18.5   | Time and Its Inversion.                                          |     |

| 18.6   | Organizing Your Toolbox                                          |     |

| 18.7   | Set Your Foundation and Move On, Out of The Box                  |     |

|        | nces                                                             |     |

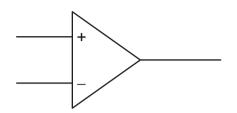

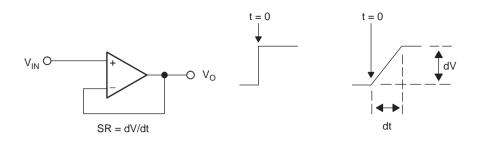

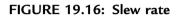

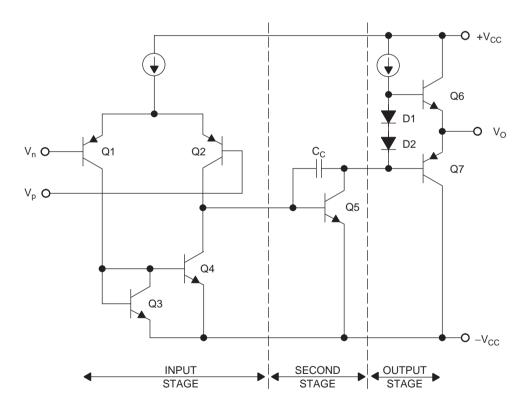

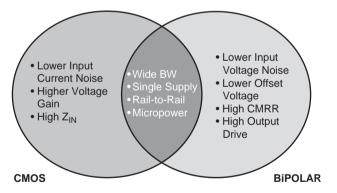

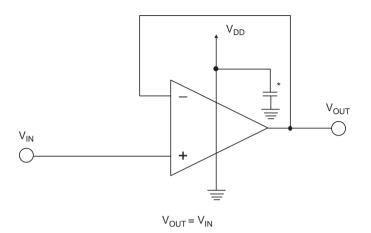

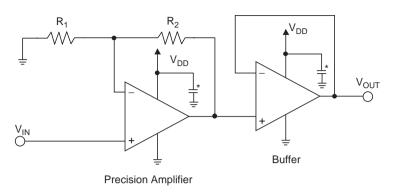

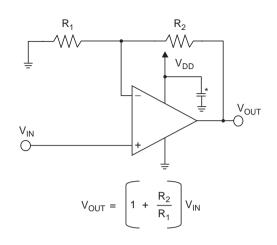

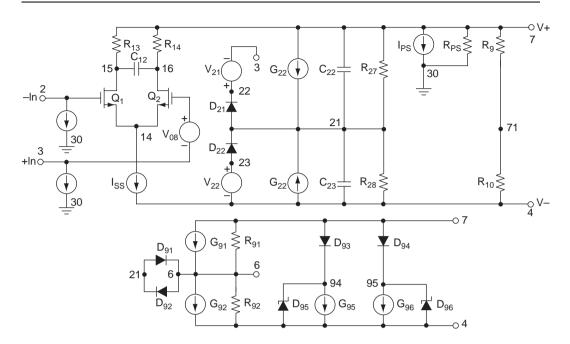

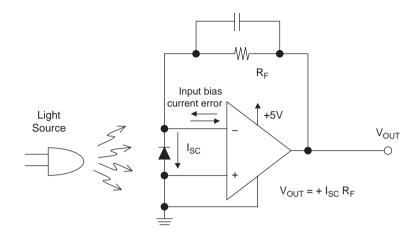

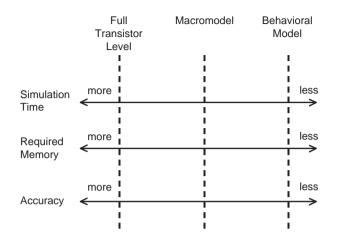

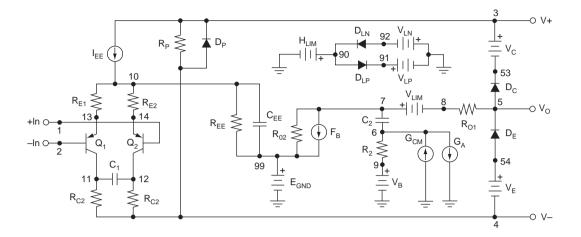

|        | r 19: Op-Amps                                                    |     |

| 19.1   |                                                                  |     |

| 19.1   | The Magical Mysterious Op-Amp<br>Understanding Op-Amp Parameters |     |

| 19.2   |                                                                  |     |

| 19.3   | Modeling Op-Amps<br>Finding the Perfect Op-Amp                   |     |

|        | rinding the reflect Op-Amp                                       |     |

| Kelele | nces                                                             |     |

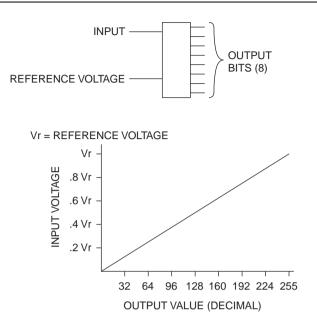

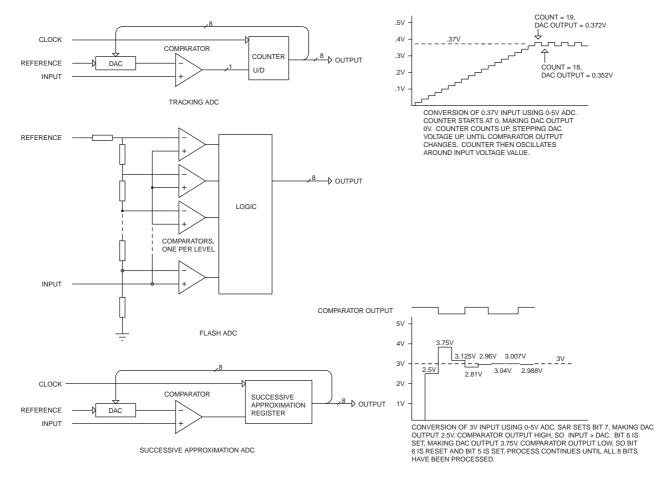

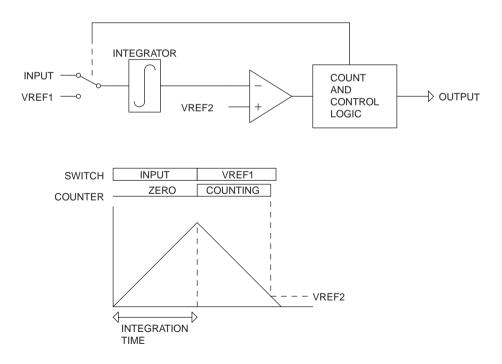

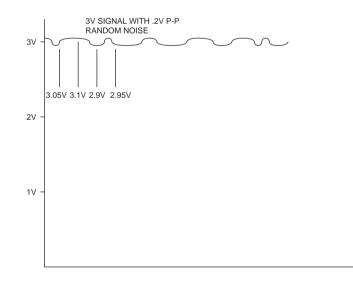

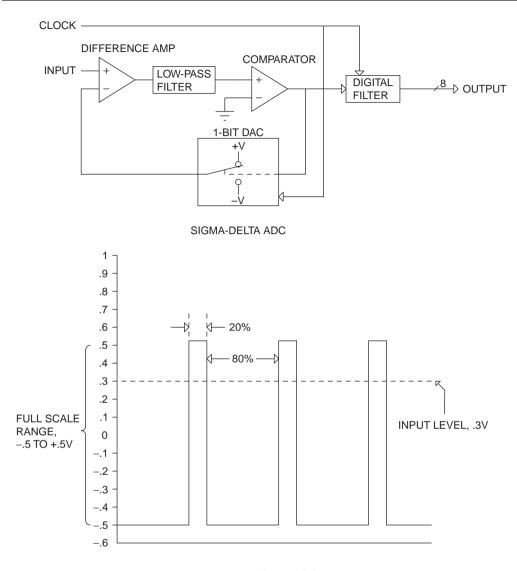

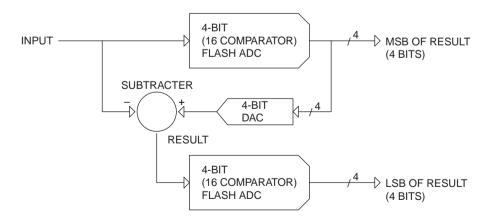

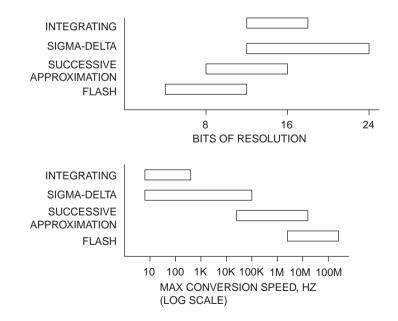

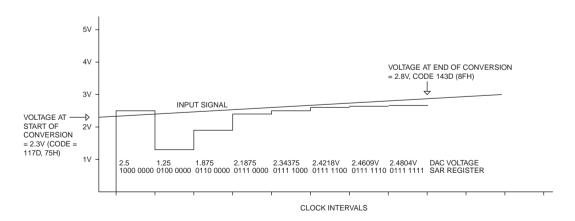

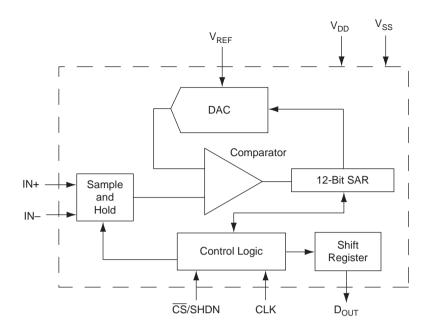

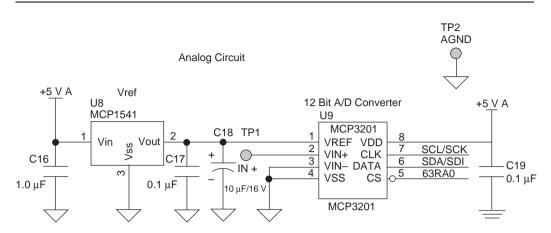

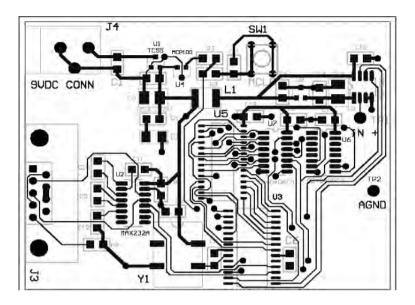

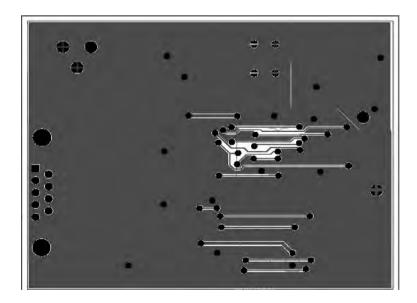

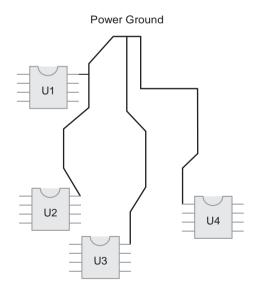

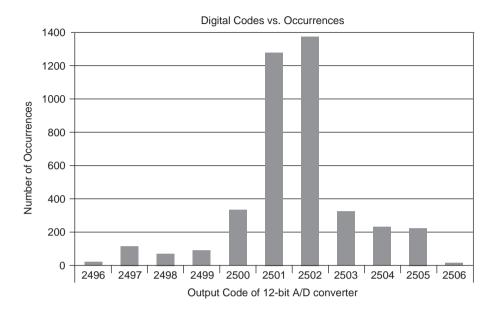

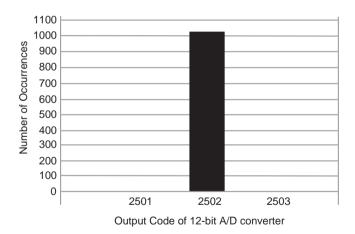

| Chapte | r 20: Analog-to-Digital Converters                               | 619 |

| 20.1   | ADCs                                                             |     |

| 20.2   | Types of ADCs                                                    |     |

| 20.3   | ADC Comparison                                                   |     |

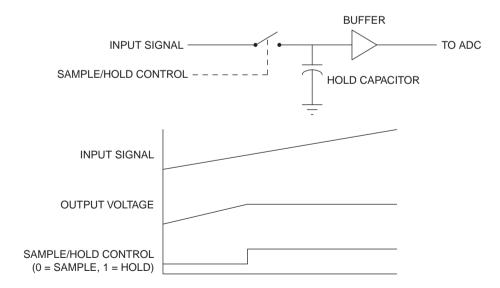

| 20.4   | Sample and Hold                                                  | 634 |

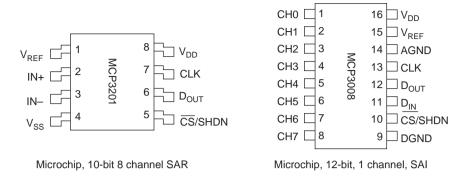

| 20.5   | Real Parts                                                       |     |

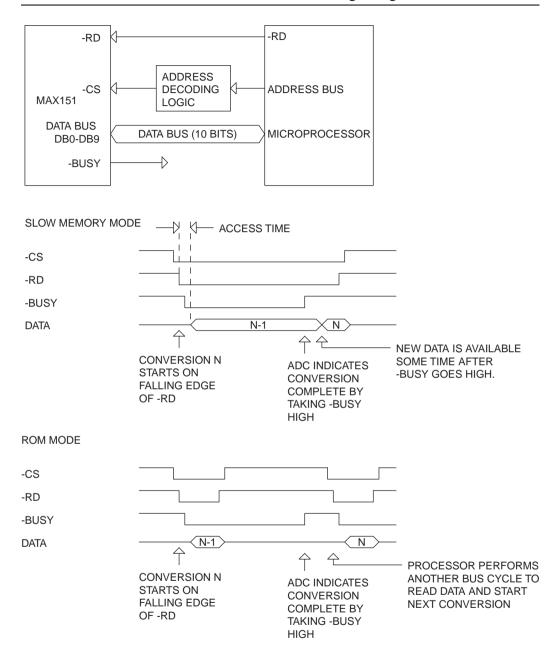

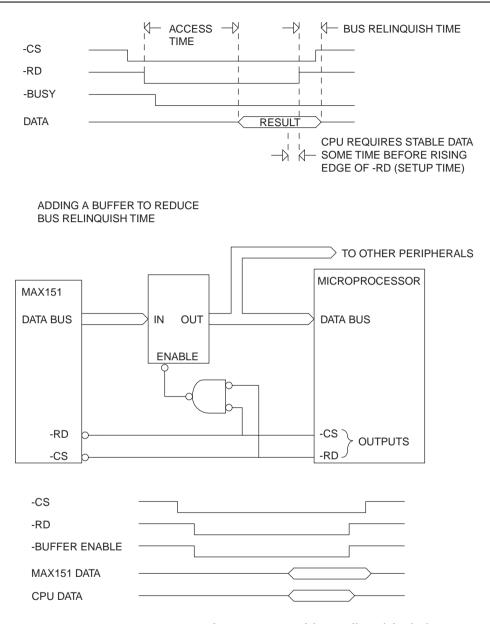

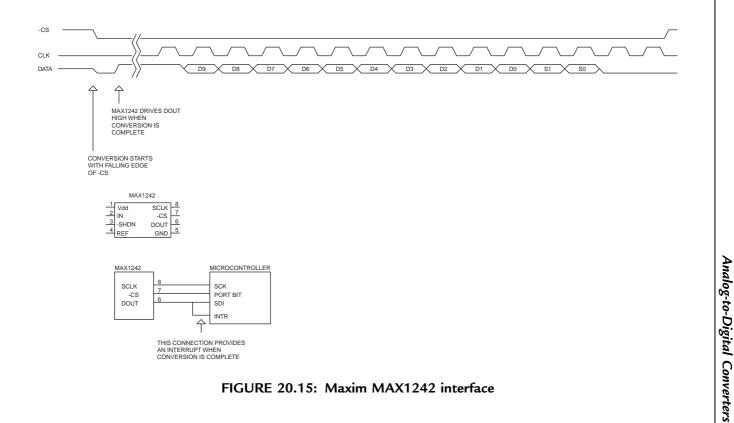

| 20.6   | Microprocessor Interfacing                                       |     |

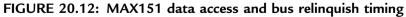

| 20.7   | Clocked Interfaces                                               |     |

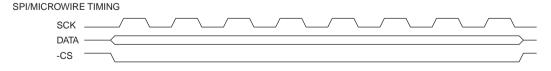

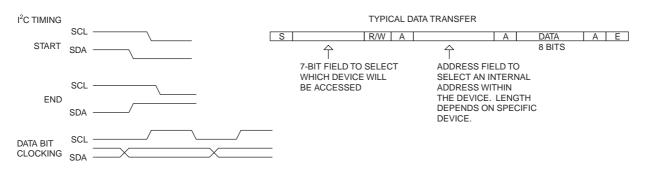

| 20.8   | Serial Interfaces                                                |     |

| 20.9   | Multichannel ADCs                                                |     |

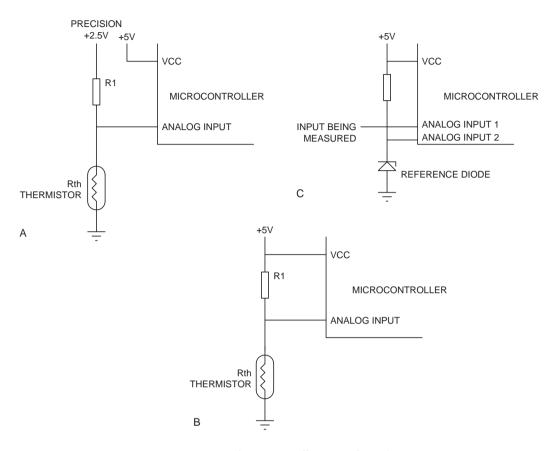

| 20.10  | Internal Microcontroller ADCs                                    |     |

| 20.11  | Codecs                                                           |     |

| 20.12  | Interrupt Rates                                                  |     |

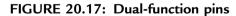

| 20.13  | Dual-Function Pins On Microcontrollers                           |     |

| 20.14  | Design Checklist                                                 |     |

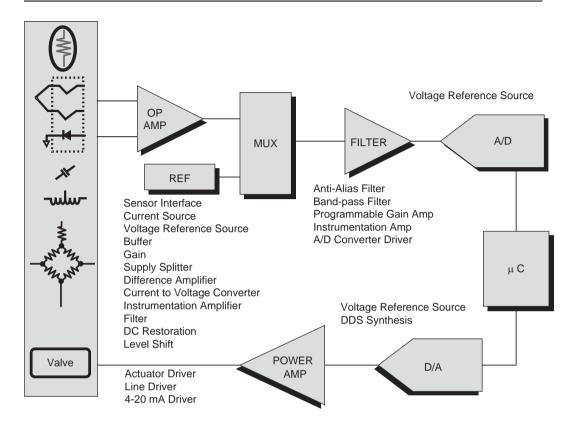

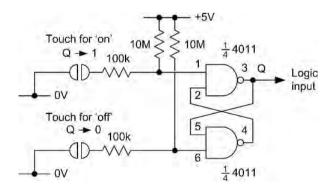

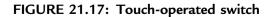

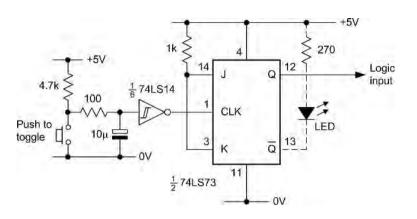

| Chapte | r 21: Sensors                                                    | 657 |

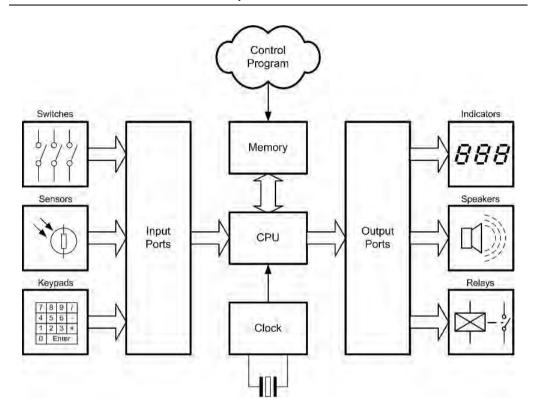

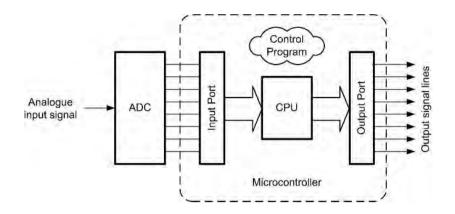

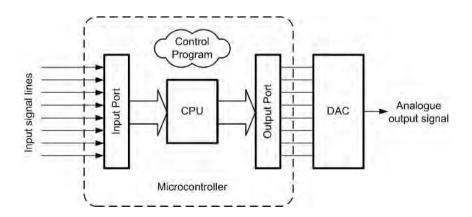

| 21.1   | Instrumentation and Control Systems                              |     |

| 21.2   | Transducers                                                      |     |

| 21.3   | Sensors                                                          |     |

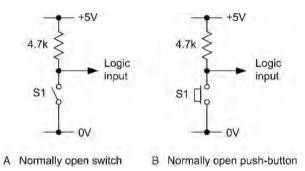

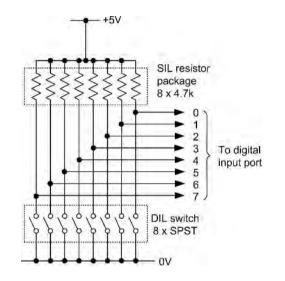

| 21.4   | Switches                                                         |     |

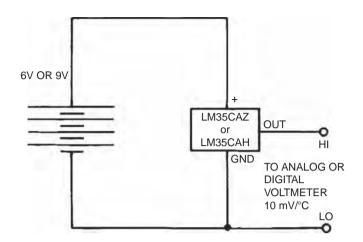

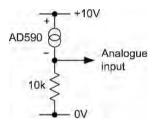

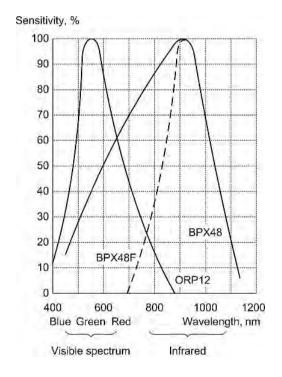

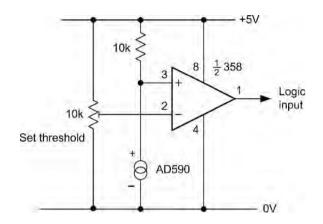

| 21.5   | Semiconductor Temperature Sensors                                |     |

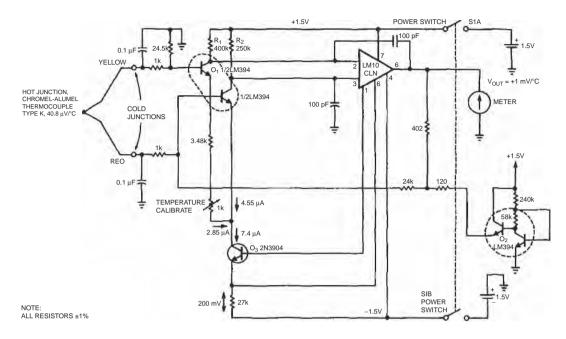

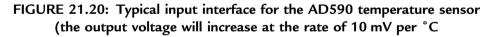

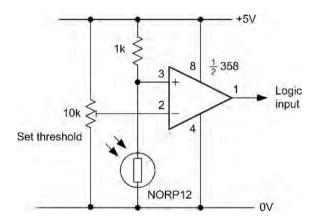

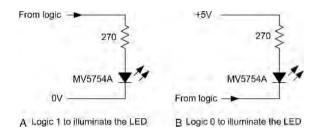

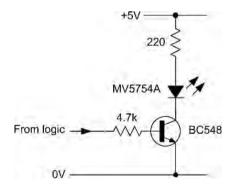

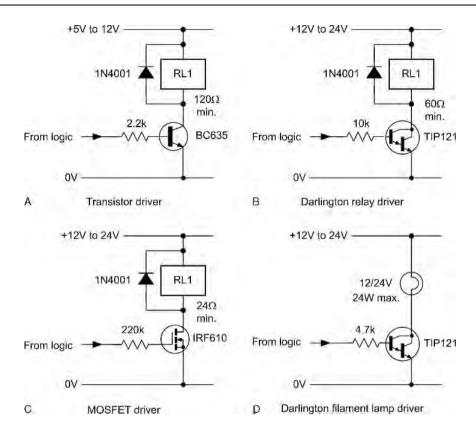

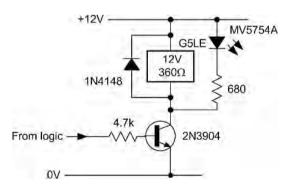

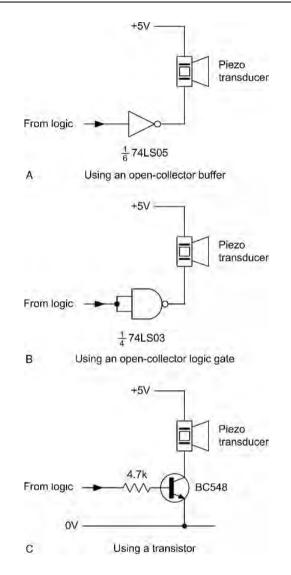

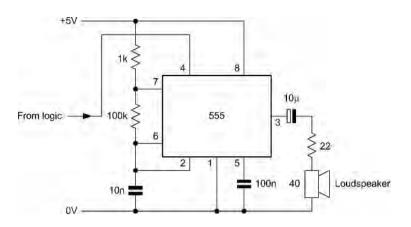

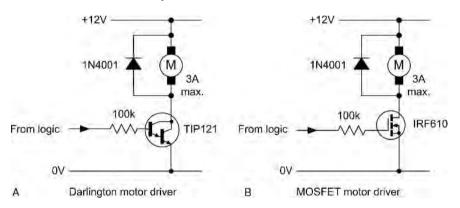

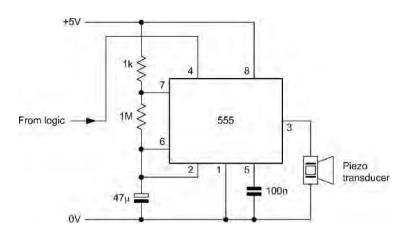

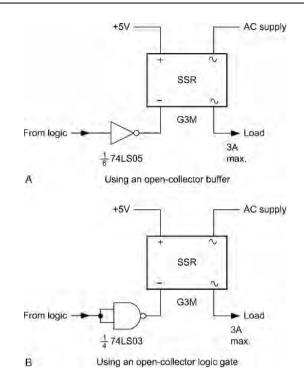

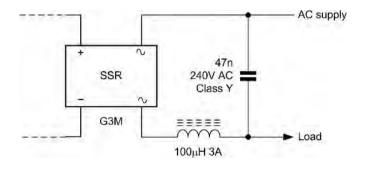

| 21.6<br>21.7<br>21.8<br>21.9<br>21.10<br>21.11<br>21.12<br>21.13                                                     | Thermocouples<br>Threshold Detection<br>Outputs<br>LED Indicators<br>Driving High-Current Loads<br>Audible Outputs<br>Motors<br>Driving Mains Connected Loads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 674<br>676<br>676<br>678<br>678<br>681                                                                |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

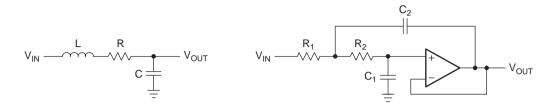

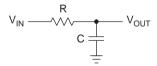

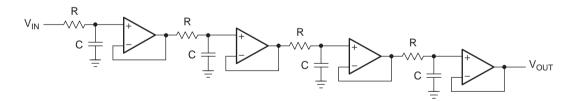

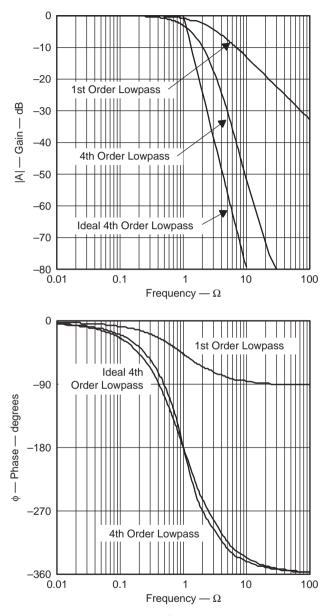

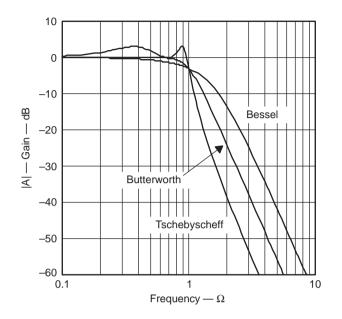

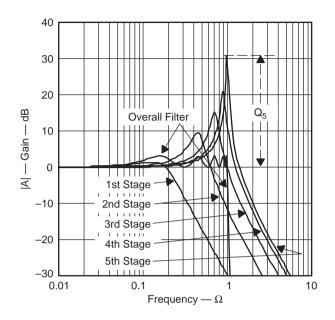

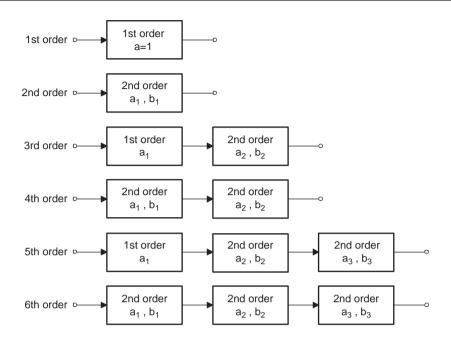

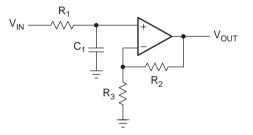

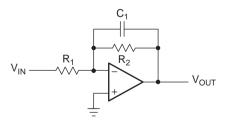

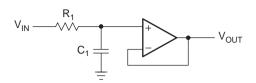

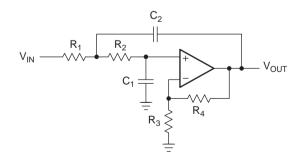

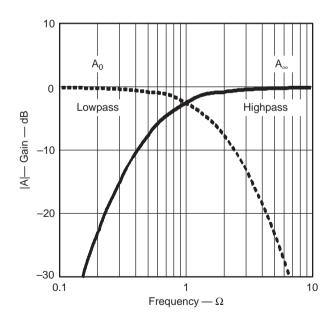

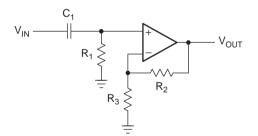

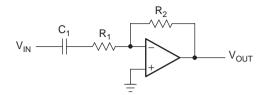

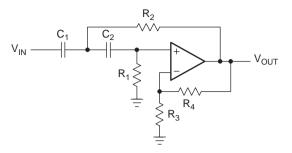

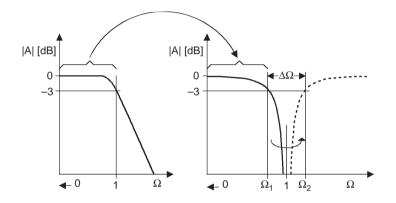

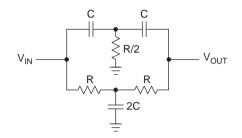

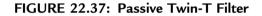

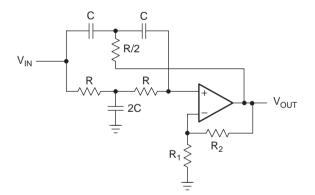

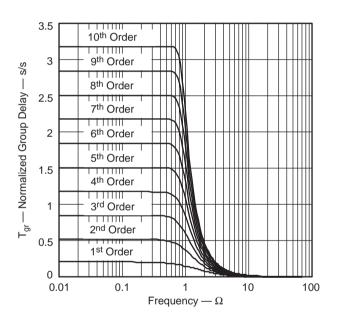

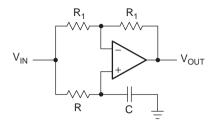

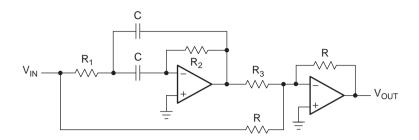

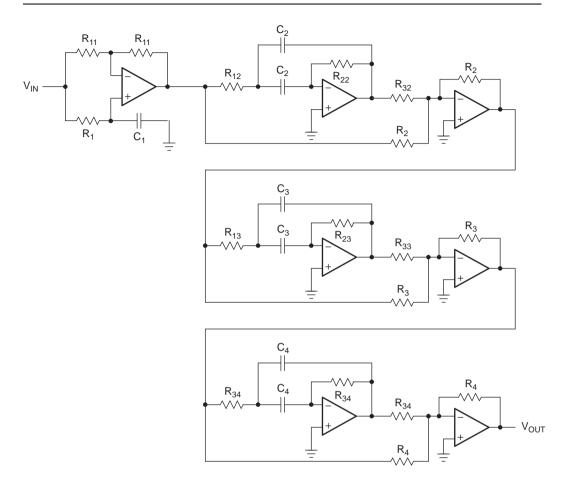

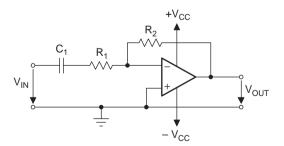

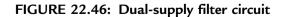

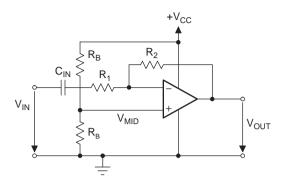

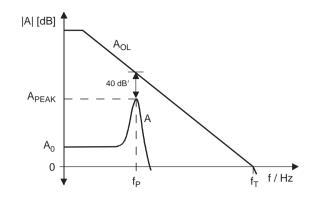

| Chapter                                                                                                              | 22: Active Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 685                                                                                                   |

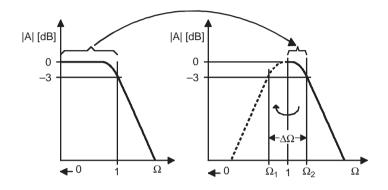

| 22.1                                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

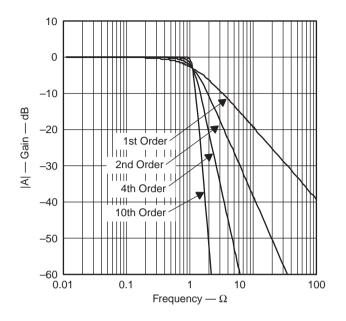

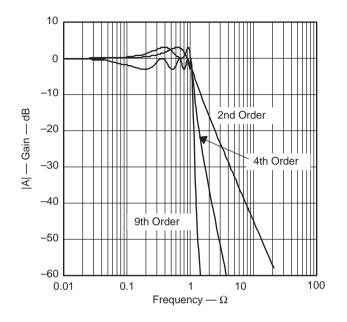

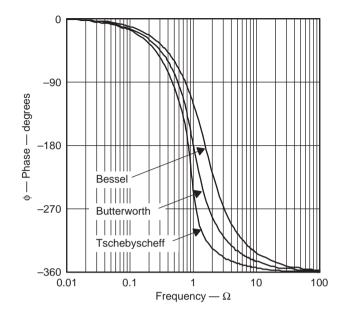

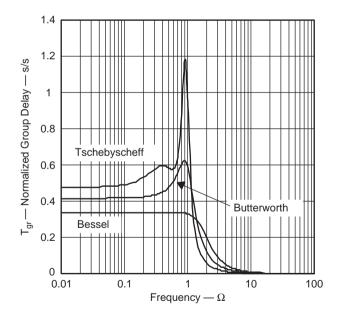

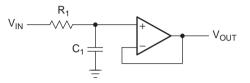

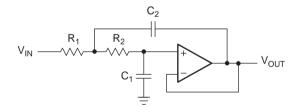

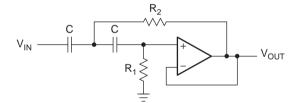

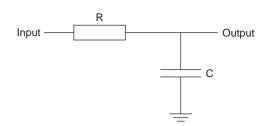

| 22.2                                                                                                                 | Fundamentals of Low-Pass Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

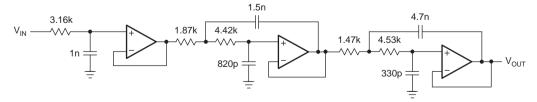

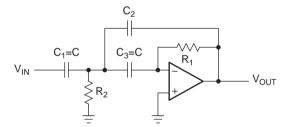

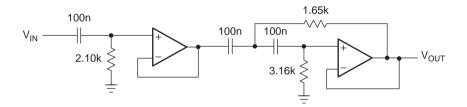

| 22.3                                                                                                                 | Low-Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 697                                                                                                   |

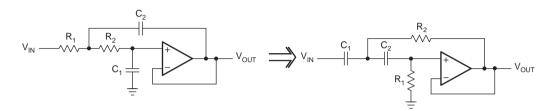

| 22.4                                                                                                                 | High-Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

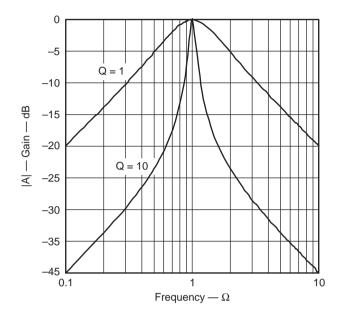

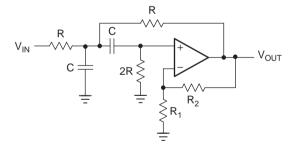

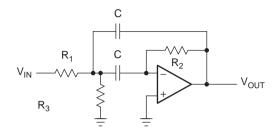

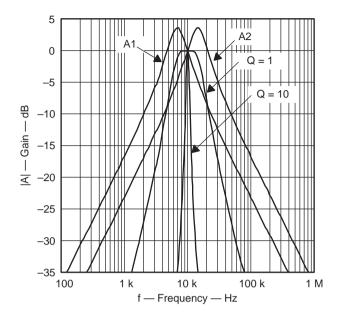

| 22.5                                                                                                                 | Band-Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 714                                                                                                   |

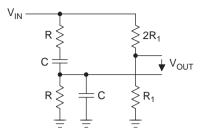

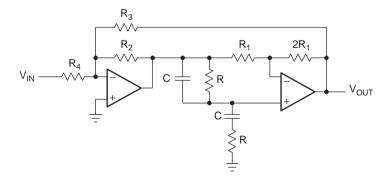

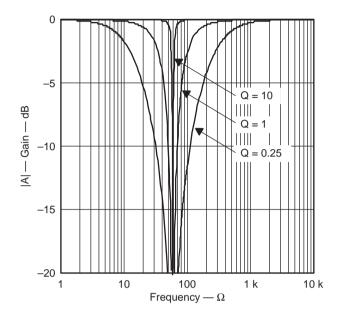

| 22.6                                                                                                                 | Band-Rejection Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

| 22.7                                                                                                                 | All-Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 22.8                                                                                                                 | Practical Design Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 22.9                                                                                                                 | Filter Coefficient Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| Referer                                                                                                              | ices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 752                                                                                                   |

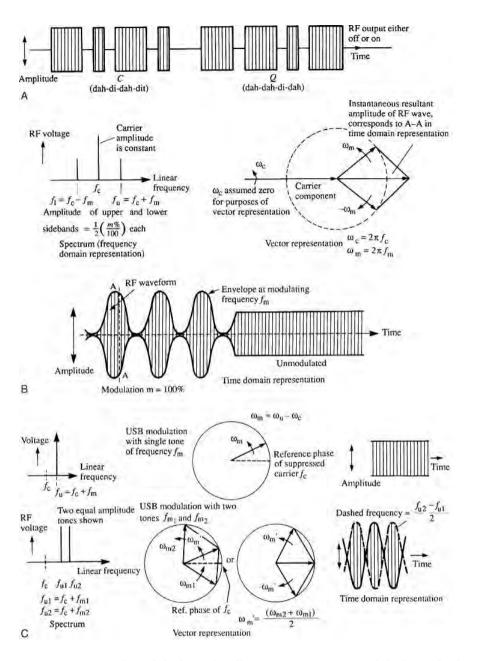

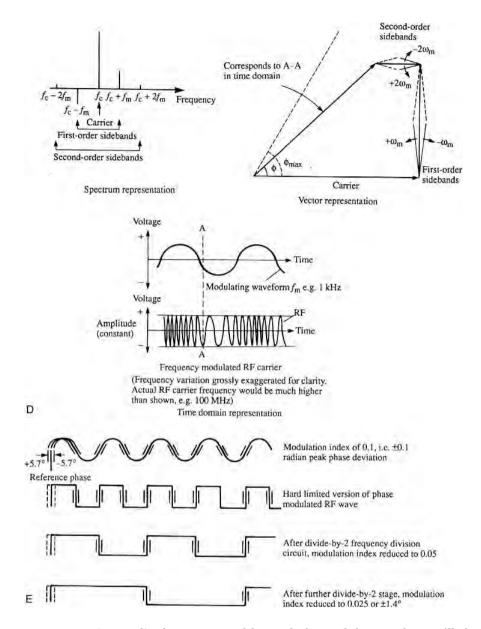

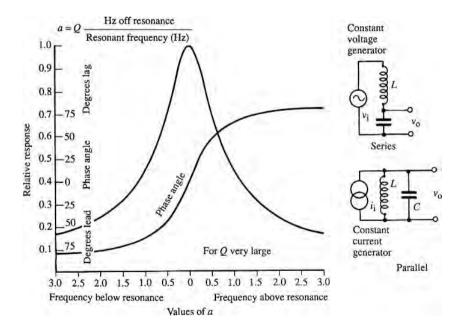

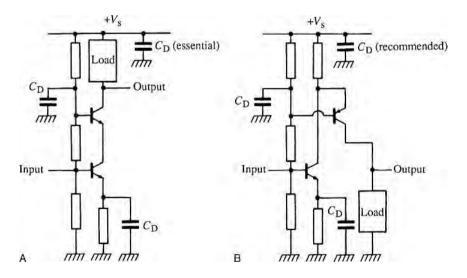

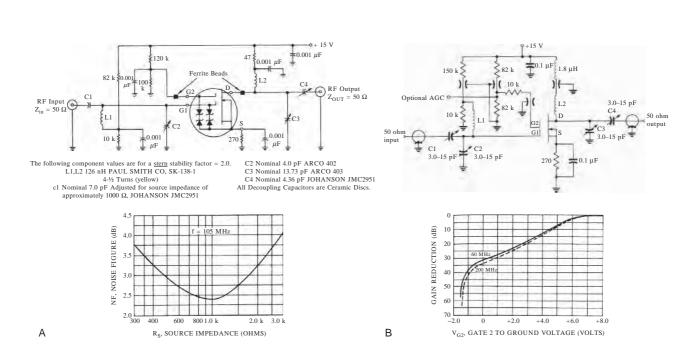

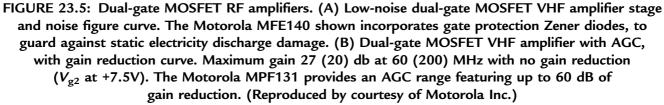

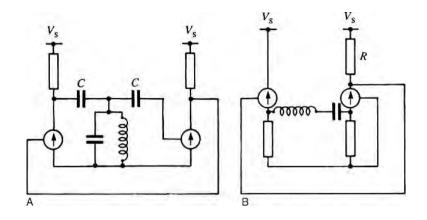

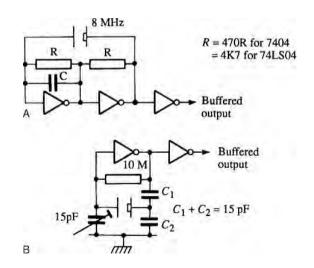

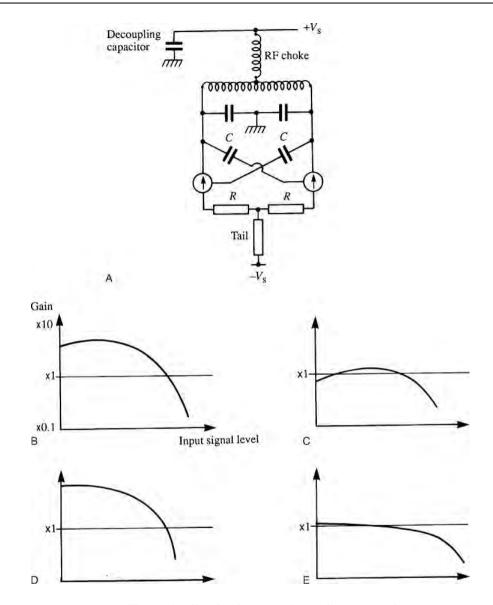

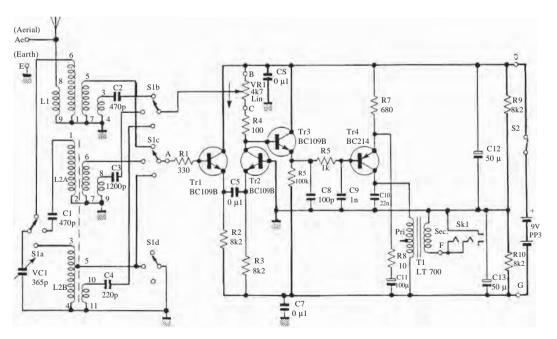

| Chapter                                                                                                              | 23: Radio-Frequency (RF) Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 753                                                                                                   |

| 23.1                                                                                                                 | Modulation of Radio Waves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

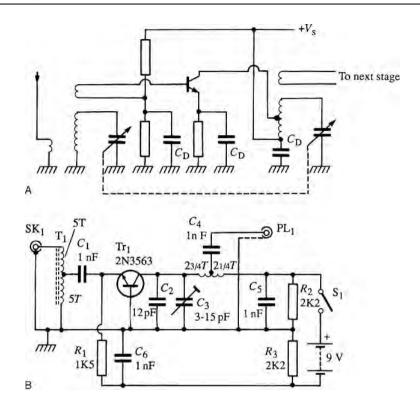

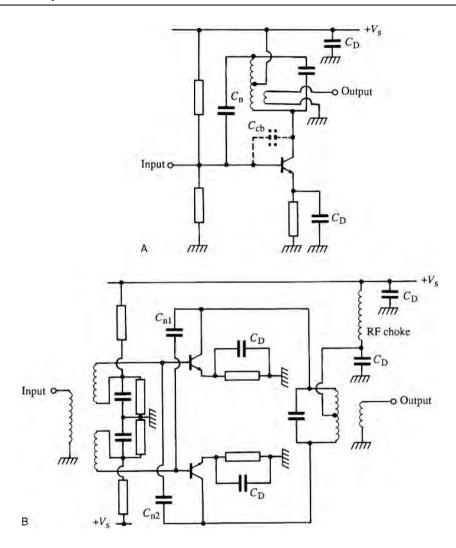

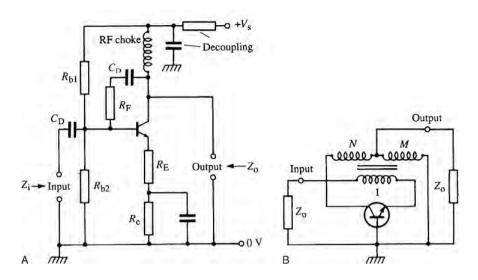

| 23.2                                                                                                                 | Low-Power RF Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

|                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| 23.3                                                                                                                 | Stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

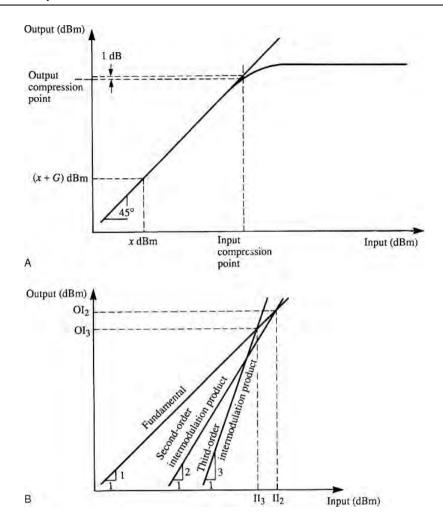

| 23.3<br>23.4                                                                                                         | Stability<br>Linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 762                                                                                                   |

| 23.3<br>23.4<br>23.5                                                                                                 | Linearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 762<br>767                                                                                            |

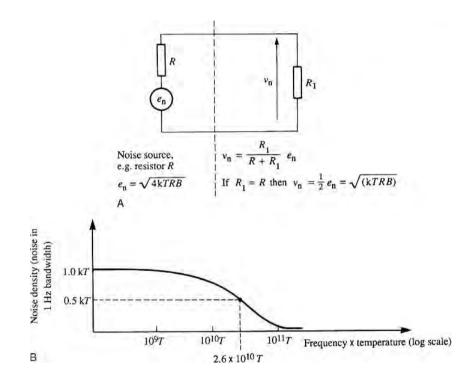

| 23.4                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 762<br>767<br>771                                                                                     |

| 23.4<br>23.5                                                                                                         | Linearity<br>Noise and Dynamic Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 762<br>767<br>771<br>773                                                                              |

| 23.4<br>23.5<br>23.6                                                                                                 | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 762<br>767<br>771<br>773<br>778                                                                       |

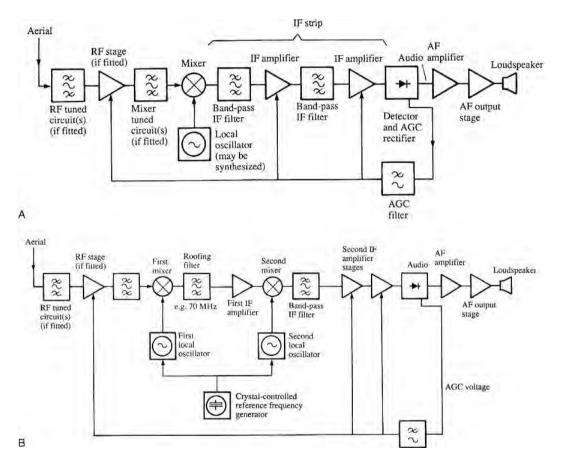

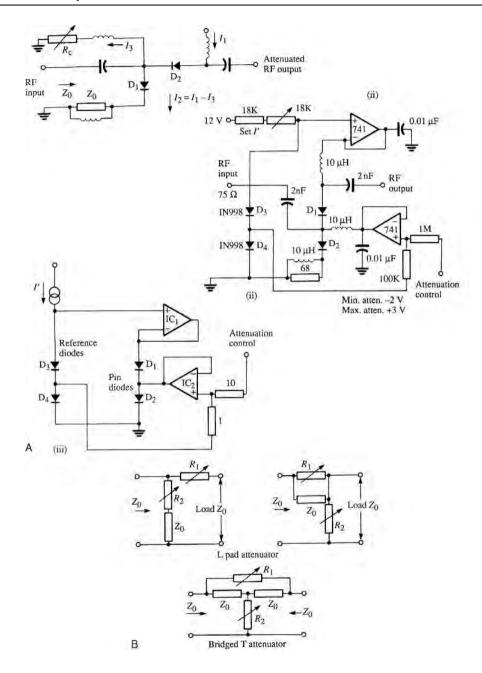

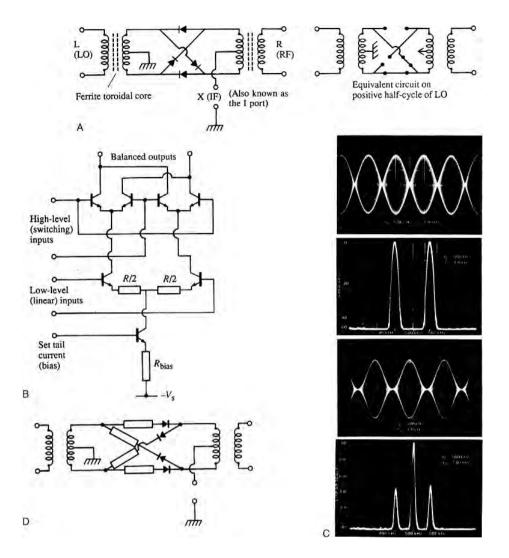

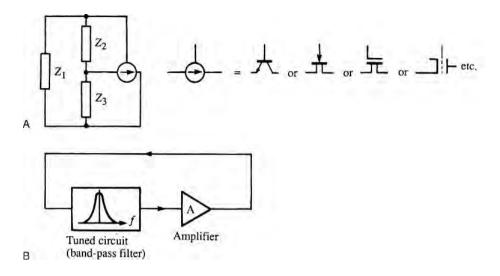

| 23.4<br>23.5<br>23.6<br>23.7                                                                                         | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 762<br>767<br>771<br>773<br>778<br>783                                                                |

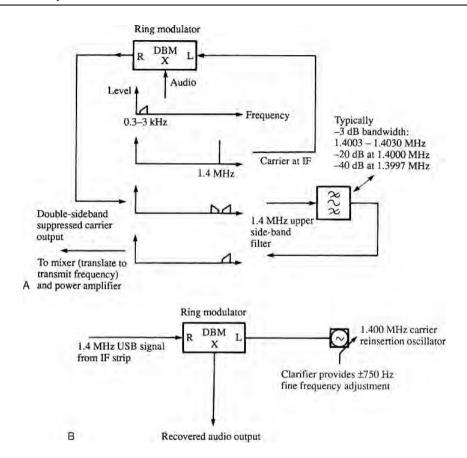

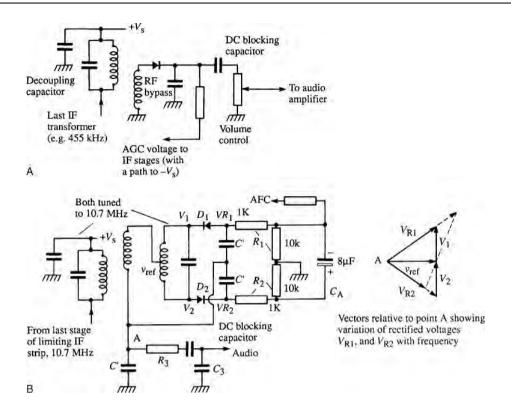

| 23.4<br>23.5<br>23.6<br>23.7<br>23.8<br>23.9                                                                         | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers<br>Demodulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 762<br>767<br>771<br>773<br>778<br>783<br>787                                                         |

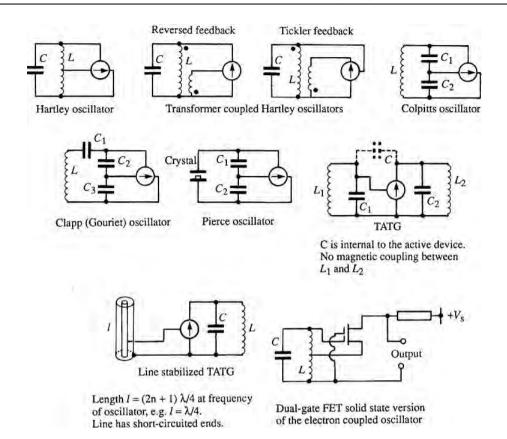

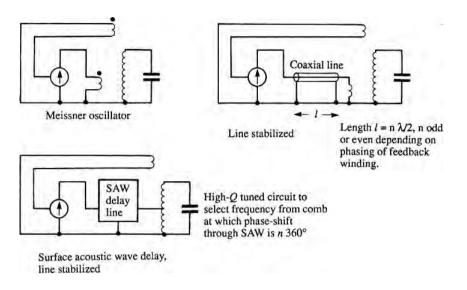

| 23.4<br>23.5<br>23.6<br>23.7<br>23.8<br>23.9<br>Referen                                                              | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers<br>Demodulators<br>Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 762<br>767<br>771<br>773<br>778<br>783<br>787<br>795                                                  |

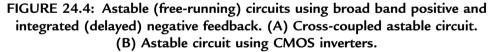

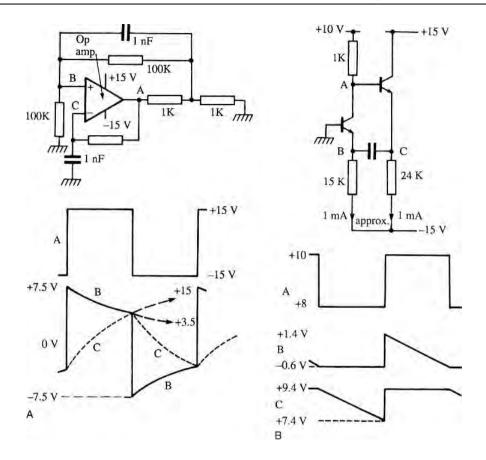

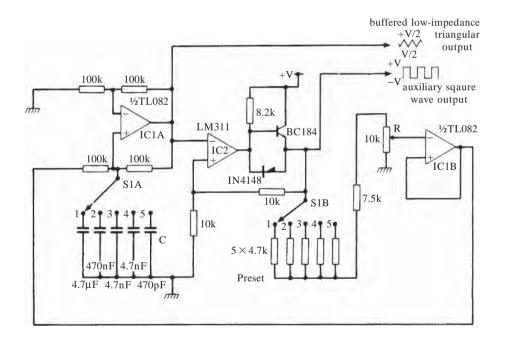

| 23.4<br>23.5<br>23.6<br>23.7<br>23.8<br>23.9<br>Referen                                                              | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers<br>Demodulators<br>Oscillators<br><b>24: Signal Sources.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 762<br>767<br>771<br>773<br>778<br>783<br>787<br>795<br><b>797</b>                                    |

| 23.4<br>23.5<br>23.6<br>23.7<br>23.8<br>23.9<br>Referen<br><b>Chapter</b><br>24.1                                    | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers<br>Demodulators<br>Oscillators<br>Oscillators<br><b>24: Signal Sources</b><br>Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 762<br>767<br>771<br>773<br>778<br>783<br>783<br>785<br>795<br>797<br>797                             |

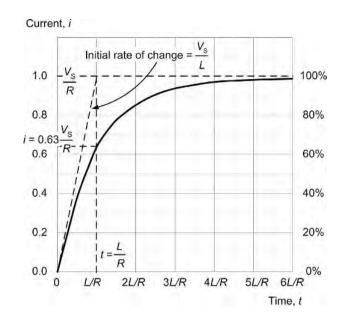

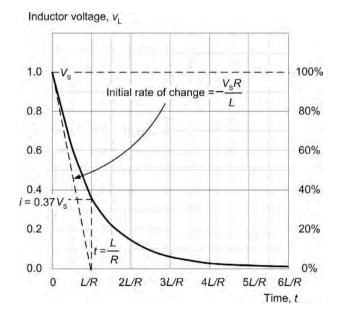

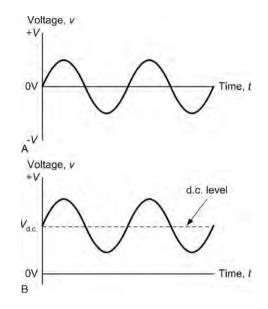

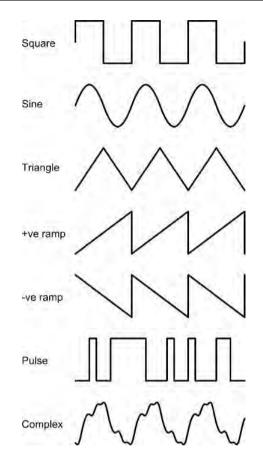

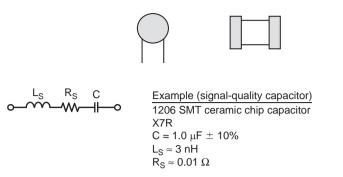

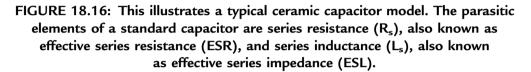

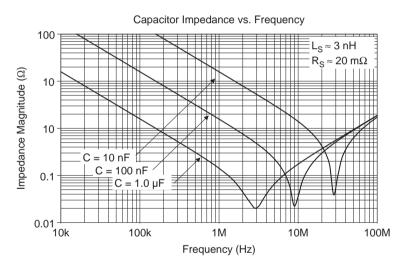

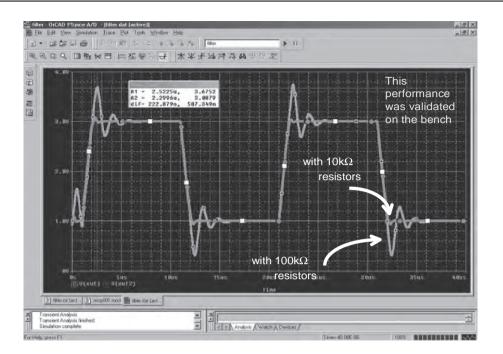

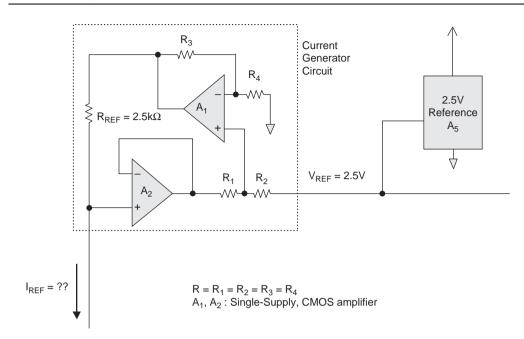

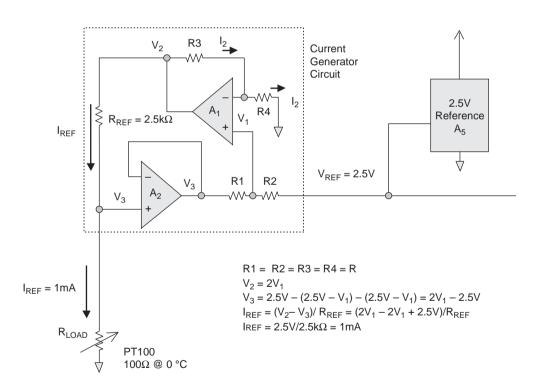

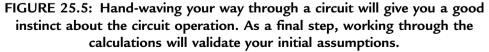

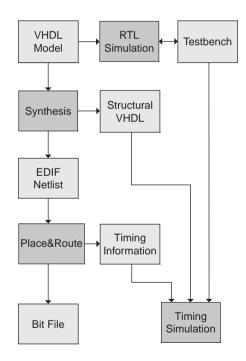

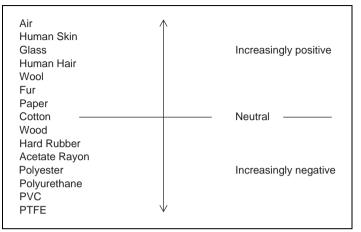

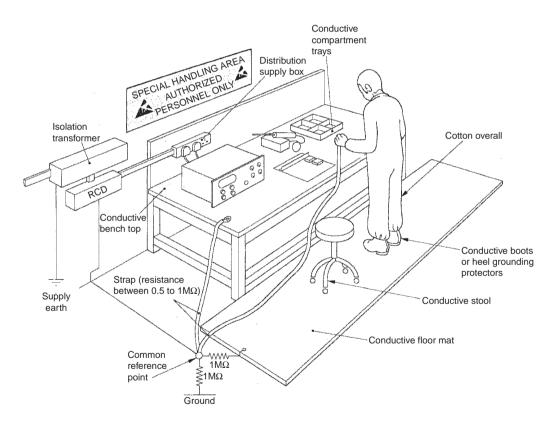

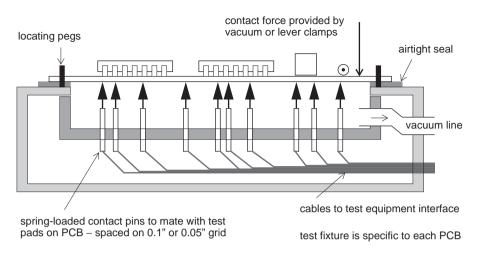

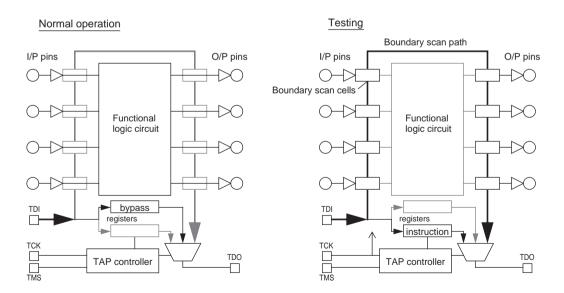

| 23.4<br>23.5<br>23.6<br>23.7<br>23.8<br>23.9<br>Referen<br>24.1<br>24.2                                              | Linearity<br>Noise and Dynamic Range<br>Impedances and Gain<br>Mixers<br>Demodulators<br>Oscillators<br>Oscillators<br><b>24: Signal Sources.</b><br>Voltage References<br>Nonsinusoidal Waveform Generators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 762<br>767<br>771<br>773<br>778<br>783<br>783<br>787<br>795<br>797<br>797<br>800                      |