#### 集成电路与智能系统创新基地测试题(2009暑期)

班级 姓名 电话 email:

#### 假似电子纸式部分

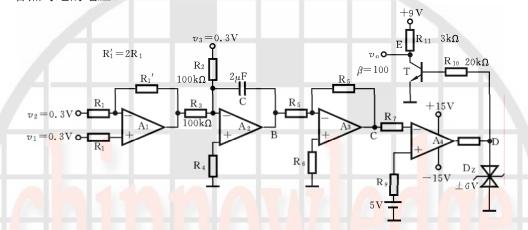

- 一、电路如图所示。设  $A_1$ ~ $A_4$  为理想运放,三极管 T 的  $V_{\text{CES}}$ =0, $I_{\text{CEO}}$ =0。

- 1. A<sub>1</sub>~A<sub>4</sub>各组成什么电路?

- 2. 设t=0时,电容器上的初始电压 $v_{\rm C}(0)=0$ 。求t=1 s 和 t=2 s 时,A、B、C、D 和 E 各点对地的电压。

### 答案:

$1. A_1$ 组成减法运算电路, $A_2$ 组成积分运算电路, $A_3$ 组成反相器, $A_4$ 组成电压比较器。

$$v_{\rm B} = -\frac{1}{C} \int_0^t (\frac{v_{\rm A}}{R_3} + \frac{v_3}{R_2}) dt$$

| t/s | $v_{\rm A}/{ m V}$ | $v_{ m B}/{ m V}$ | $v_{\rm C}/{ m V}$ | $v_{ m D}/{ m V}$ | $v_{\rm E}/{ m V}$ |

|-----|--------------------|-------------------|--------------------|-------------------|--------------------|

| 1   | 0.3                | -3                | 3                  | 6                 | 0                  |

| 2   | 0.3                | -6                | 6                  | -6                | 9                  |

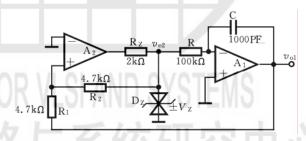

- 二、电路如图所示, $A_1$ 、和  $A_2$  均为理想器件, $V_z=5V_s$ 。

- 1. 试画出 $v_{ol}$ 及 $v_{o2}$ 的波形(注意相位关系):

- 2. 求出的 $v_{o1}$ 和 $v_{o2}$ 幅值;

- 3. 求出 <sup>v</sup>。1 的周期。

### 答案:

- 1.  $v_{o2}$  为方波, $v_{o1}$  为三角波( $v_{o2}$  为高电平时, $v_{o1}$  由正向负方向变;反之, $v_{o1}$  由负向正方向变)

- 2.  $v_{\rm ol}$ 、 $v_{\rm o2}$ 的幅值都为±5V

- 3. vol 的周期 T=0.2ms

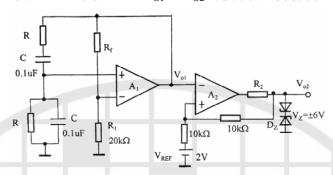

三、

电路如图所示, A<sub>1</sub>、A<sub>2</sub>为理想运放。

- 1. 为使电路满足起振的幅值条件, $R_f$ 应如何选择?

- 2. 为使电路产生 100Hz 的正弦波振荡, R 应该选多大?

- 3. 现有一个具有正温度系数的热敏电阻  $R_f$ ,为了稳幅,可将它替换哪个电阻(假设它与被替换电阻的阻值相同)?

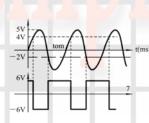

- 4. 若  $V_{O1}$  的峰值等于 5V,试对应画出  $V_{O1}$  和  $V_{O2}$  的波形图,并标明它们的幅值。

#### 答案:

$$A_{\rm V} = 1 + \frac{R_{\rm f}}{R_{\rm l}} \ge 3$$

$$\frac{R_f}{R_1} \ge 2$$

$$R_f \ge 2R_1 = 40K$$

$$f = \frac{1}{2\pi RC}$$

$$R = \frac{1}{2\pi cf} = \frac{1}{2\pi \times 0.1 \times 10^{-6} \times 100} = 15.9 = 16(K\Omega)$$

3. 替换 R1

$$V_{01} = V_{P2} = \frac{1}{2} \times 2V + \frac{1}{2} \times (\pm 6V) = 1V \pm 3V$$

$$\therefore V_{\text{th}1} = 4V \qquad V_{\text{th}2} = -2V$$

# **劉字电子脏术部分**

四、如图所示,为检测水箱的液位,在 A、B、C、三个地方安置了三个水位检测元件,当水面低于检测元件时,检测元件输出低电平,水面高于检测元件时,检测元件输出高电平。试用与非门设计一个水位状态显示电路,要求: 当水面在 A、B 之间的正常状态时,仅绿灯 G亮; 水面在 B、C 间或 A 以上的异常状态时,仅黄 Y 灯亮; 水面在 C 以下的危险状态时,仅红灯 R 亮。

#### 答案:

真值表如表所示,各逻辑函数的与非-与非表达式分别为

$$R = \overline{C}$$

逻辑图略。

$$Y = A + \overline{BC} = \overline{A \cdot \overline{BC}}$$

$$G = \overline{\overline{AB}}$$

|   |   |   | 表 |   |                  |   |

|---|---|---|---|---|------------------|---|

| A | В | C | R | Y | $\boldsymbol{G}$ |   |

| 0 | 0 | 0 | 1 | 0 | 0                | _ |

| 0 | 0 | 1 | 0 | 1 | 0                |   |

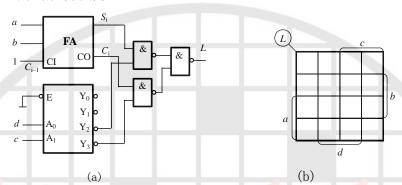

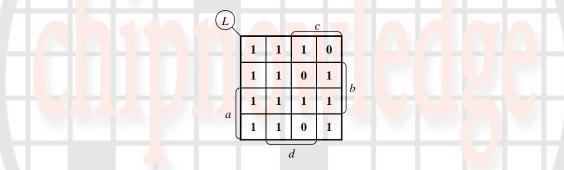

五、发由全加器 FA、2-4 线译码器和门电路组成的逻辑电路如图 a 所示。试在图 b 中填写输出逻辑函数 L 的卡诺图并化简。

#### 答案:

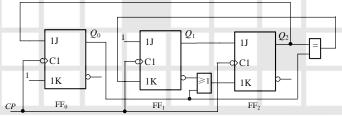

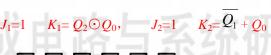

六、逻辑电路如图 4 所示, 试画出  $Q_0$ 、 $Q_1$ 、 $Q_2$ 的波形。设各触发器初态为  $\mathbf{0}$ 。

# 答案:

驱动方程:  $J_0=Q_2$   $K_0=1$ , 波形图如图 A4。

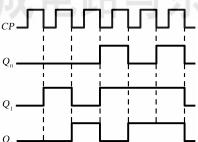

七、由 555 定时器组成的脉冲电路及参数如图 8 a 所示。已知  $v_1$  的电压波形如图 b 所示。试对应  $v_1$  画出图中  $v_{O1}$ 、 $v_{O2}$  的波形;

RESEARCH CENTER FOR VLSI AND SYSTEMS 超大规模集成电路与系统研究中心

### 电路理论部分

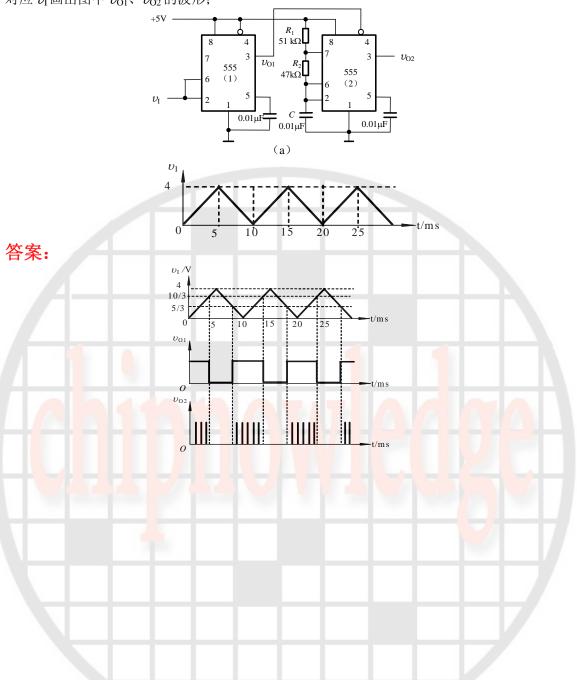

八、如下图示含理想运算放大器电路,试计算电路的电压增益 $u_o/u_i$ 。

答案:

解:

$$\begin{cases} \frac{u_i - u_1}{2000} = \frac{u_1 - u_2}{2000} + \frac{u_1 - u_o}{4000} \\ \frac{u_2 - u_3}{4000} = \frac{u_3}{1000} \\ u_1 = 0 \\ u_3 = u_o \end{cases}$$

解得,

$$\frac{u_o}{u_i} = -\frac{2}{11}$$

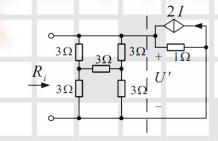

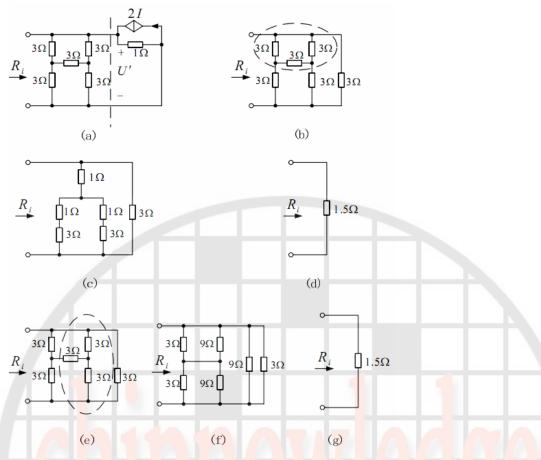

九、求如下图所示的一端口网络的输入电阻

答案:

RESEARCH CENTER FOR VLSI AND SYSTEMS 超大规模集成电路与系统研究中心

解:将图中所示虚线处断开,采用附加电源法求虚线右侧二端网络的输入电阻  $R'_i$ ,这里附

加电源为电压源,则有 $U'=(I+2I)\times 1$ ,所以 $R'_i=\frac{U'}{I}=3\Omega$ 。这样,原电路可化简为图 3

(b),再进行如图 3 (c) 和 (d) 的化简过程后,可得  $R_i = 1.5\Omega$  。 也可采用另一种化简过程,如图 3 (e)、(f) 和 (g) 所示。

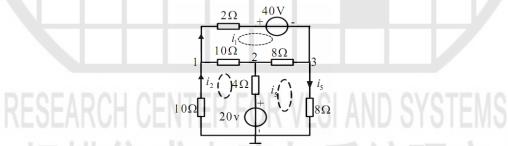

十、采用节点电压法计算下左图电路的电流。

解: 网孔电流参考方向及参考节点如图中所示。 网孔电流方程为

$$20i_1 - 10i_2 - 8i_5 = -40$$

$$-10i_1 + 24i_2 - 4i_5 = -20$$

$$-8i_1 - 4i_2 + 20i_5 = 20$$

i<sub>5</sub> =-0. 956A 解方程组得

节点电压方程为

$$0.7\Phi_1 - 0.1\Phi_2 - 0.5\Phi_3 = 20$$

$$-0.1\Phi_1 + 0.475\Phi_2 - 0.125\Phi_3 = 5$$

$$-0.5\Phi_1 - 0.125\Phi_2 + 0.72\Phi_3 = -20$$

解方程组的 $\Phi$ 3 = -0.746V

$$i_5 = \Phi_3 / 8 = -0.956 A$$

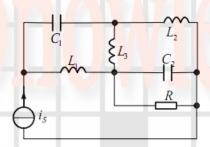

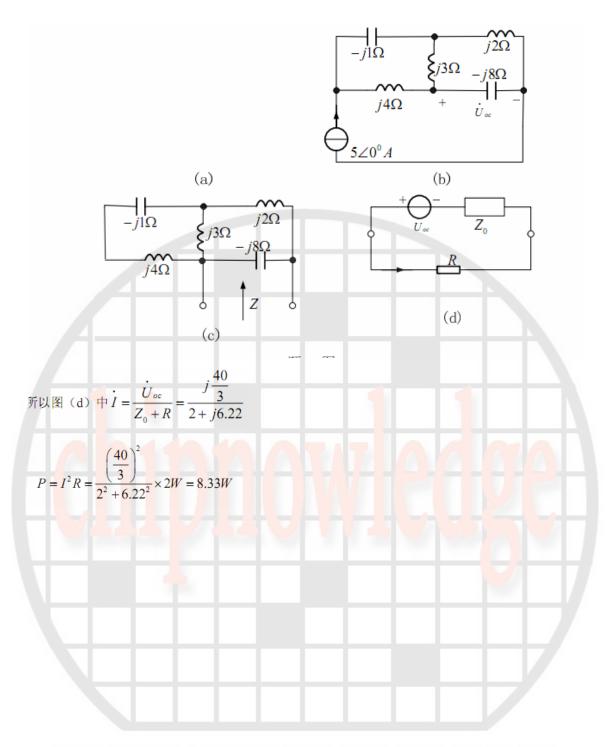

十一、 正弦稳态电路如图 所示, $i_s = 5\sqrt{2}\sin 5 \times 10^4 tA$ , $C_1 = 20\mu F$ , $C_2 = 2.5\mu F$ , $5\mu F$ ,  $L_1 = 0.08mH$  ,  $L_2 = 0.04mH$  ,  $L_3 = 0.06mH$  ,  $R = 2\Omega$  。求 R 吸收的有功功率。

# 答案:

解:根据 R 与其他元件的联接方式,本例用戴维南定理求解:

$$X_{L1} = \omega L_1 = 5 \times 10^4 \times 0.08 \times 10^{-3} = 4\Omega$$

$$X_{L2} = \omega L_2 = 5 \times 10^4 \times 0.04 \times 10^{-3} = 2\Omega$$

$$X_{L3} = \omega L_3 = 5 \times 10^4 \times 0.06 \times 10^{-3} = 3\Omega$$

$$X_{C1} = \frac{1}{\omega C_1} = \frac{1}{5 \times 10^4 \times 20 \times 10^{-6}} = 1\Omega$$

$$X_{L3} = \omega L_3 = 5 \times 10^4 \times 0.06 \times 10^{-3} = 3\Omega$$

$$X_{C1} = \frac{1}{\omega C_1} = \frac{1}{5 \times 10^4 \times 20 \times 10^{-6}} = 1\Omega$$

$$X_{C2} = \frac{1}{\omega C_2} = \frac{1}{5 \times 10^4 \times 2.4 \times 10^{-6}} = 8\Omega$$

图 (d) 戴维南等效电路中, $U_{\infty}$  及 $Z_0$  的求解分别如图 (b)、(c) 所示。图 (b) 中,平衡 电桥电路  $j2 \times j4 = (-j) \times (-j8)$

$$\dot{U}_{oc} = \frac{5(-j+j2)}{(j4-j8)+(-j+j2)} \times (-j8)V = j\frac{40}{3}V$$

RESEARCH CENTER FOR VLSI AND SYSTEMS 超大规模集成电路与系统研究中心

# 歌字电路投货与 加西部分

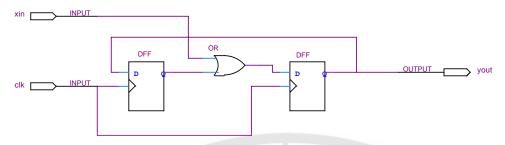

十二、看下面原理图,写出相应 VHDL 描述

#### 答案:

```

LIBARRY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MYCIR IS

```

END MYCIR;

ARCHITECTURE ONE OF MYCIR IS

SIGNAL A, B, C;

BEGIN

B <= XIN OR A;

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN

A <= C; C <= B;

END IF;

END PROCESS;

YOUT <= C;

#### END ONE;

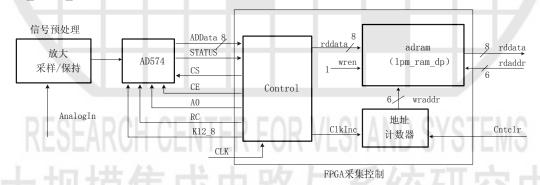

十三、下图是一个 A/D 采集系统的部分,要求设计其中的 FPGA 采集控制模块,该模块由三个部分构成:控制器(Control)、地址计数器(addrcnt)、内嵌双口 RAM(adram)。控制器(control)是一个状态机,完成 AD574 的控制,和 adram 的写入操作。adram 是一个LPM\_RAM\_DP 单元,在 wren 为'1'时允许写入数据。试分别回答问题

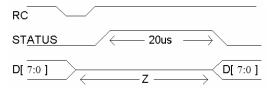

下面列出了 AD574 的控制方式和控制时序图:

AD574 逻辑控制真值表(X表示任意)

| CE | CS | RC | K12_8 | A0 | 工作状态       |

|----|----|----|-------|----|------------|

| 0  | X  | X  | X     | X  | 禁止         |

| X  | 1  | X  | X     | X  | 禁止         |

| 1  | 0  | 0  | X     | 0  | 启动 12 位转换  |

| 1  | 0  | 0  | X     | 1  | 启动 8 位转换   |

| 1  | 0  | 1  | 1     | X  | 12 位并行输出有效 |

| 1 | 0 | 1 | 0 | 0 | 高 8 位并行输出有效  |

|---|---|---|---|---|--------------|

| 1 | 0 | 1 | 0 | 1 | 低4位加上尾随4个0有效 |

AD574 工作时序

#### 问题:

- 1. 要求 AD574 工作在 8 位转换模式, K12\_8、A0 在 control 中如何设置?

- 2. 试画出 control 的状态机的状态图

- 3. 地址计数器每当 ClkInc 时钟上升沿到达,输出地址加 1,请对该模块进行 VHDL 描述。

- 4. 根据状态图,试对 control 进行 VHDL 描述

#### 答案:

1、K12\_8 低电平; A0 高电平

```

S0

初始化

采样数据锁存

启动A/D转换

S3

数据输出有效

采样等待

status = '1'

status = '0'

2,

Library ieee;

Use ieee. std_logic_1164. all;

Use ieee.std_logic_unsigned.all;

```

```

Entity cnt64 is

```

```

Port ( ClkInc, Cntclr : in std_logic; — 时钟信号和清零信号输入

Wraddr : out std_logic_vector (5 downto 0));

End cnt64;

```

```

Architecture one of cnt64 is

Begin

Process (clkinc, cntclr)

Variable counter : std_logic_vector (5 downto 0);

If cntclr = '1' then counter := (others => '0');

Elsif clkinc = '1' and clkinc'event then counter := counter + 1;

End if;

```

```

Wraddr <= counter;

End process;

End one;

4、

Library ieee;

Use ieee. std_logic_1164. all;

Use ieee.std_logic_unsigned.all;

Entity control is

-- 时钟信号和AD转换状态信号输入

Port ( CLK, STATUS : in std_logic;

: in std logic vector (7 downto 0); -- 转换数据输入

CS, CE, AO, RC, K12 8 : out std logic;

-- AD574控制信

문

: out std logic; — 地址计数器时钟信号

ClkInc

rddata

: out std_logic_vector (7 downto 0)); -- 转换数据输出

End control:

Architecture behave of control is

Type sm_state is (s0, s1, s2, s3, s4);

Signal c_st, n_st : sm_state;

Signal lock : std_logic;

Signal regdata : std_logic_vector(7 downto 0);

Begin

K12_8 <= '0';

A0 <= '1';

Process (clk)

If clk'event and clk = '1' then c_st <= n_st; end if;

Process (c_st, status)

Begin

Case c_st is

When s0 => n st <= s1; rc <= '1'; ce <= '0'; cs <= '1'; lock <= '0';

When s1 => n st <= s2; rc <= '0'; ce <= '1'; cs <= '0; lock <= '0';

When s2 => if status = '0' then n_st <= s3; else n_st <= s2;

Rc <= '1'; ce <= '1' cs <= '0'; lock <= '0';

When s3 => n_st <= s4; rc <= '1'; ce <= '1'; cs <= '0'; lock <=

When s4 => n_st <= s0; rc <= '1'; ce <= '1'; cs <= '0'; lock <=

When others => n_st <= s0;

End case;

End process;

Process (lock)

Begin

If lock'event and lock = '1' then

Regdata <= addata;

Clkinc <= '1';

Else

End if;

End process;

Rddata <= regdata;

End behave;

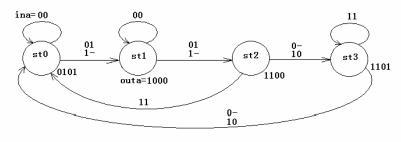

十四、已知状态机状态图如图(a)所示; 完成下列各题:

```

图(a) 状态图

- 1. 试判断该状态机类型,并说明理由。

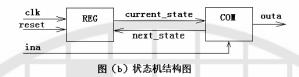

- 2.根据状态图,写出对应于结构图(b),分别由主控组合进程和主控时序进程组成的 VHDL 有限状态机描述

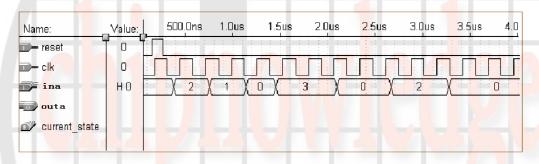

- 3.若已知输入信号如下图所示,分析状态机的工作时序,画出该状态机的状态转换值 (current\_state) 和输出控制信号(outa);

4.若状态机仿真过程中出现毛刺现象,应如何消除;试指出两种方法,并简单说明其原理。

#### 答案:

1、 该状态机为 moore 型状态机,输出数据 outa 和输入 ina 没有直接逻辑关系,outa 是时  $\phi$  clk 的同步时序逻辑。

2,

```

Library ieee;

Use ieee.std_logic_1164.all;

Entity mooreb is

Port (clk, reset : in std_logic;

Ina : in std_logic_vector (1 downto 0);

Outa : out std_logic_vector (3 downto 0) );

End mooreb;

Architecture one of mooreb is

Type ms_state is (st0, st1, st2, st3);

Signal c_st, n_st : ms_state; in

Begin

Process (clk, reset)

Begin

If reset = '1' then c_st <= st0;</pre>

Elsif clk'event and clk = '1' then c_st <= n_st;</pre>

End if;

End process;

Process (c_st)

Begin

Case c_st is

```

```

When st0 \Rightarrow if ina = "00" then n_st <= st0;

Else n_st <= st1;</pre>

End if;

Outa <= "0101";

When st1 => if ina = "00" then n_st <= st1;

Else n_st <= st2;</pre>

End if;

Outa <= "1000";

When st2 \Rightarrow if ina = "11" then n_st <= st0;

Else n_st <= st3;</pre>

End if;

Outa <= "1100";

When st3 => if ina = "11" then n_st <= st3;

Else n st <= st0;</pre>

End if;

Outa <= "1101";

When others => n_st <= st0;

End case;

End process;

End one;

ΗО

reset

но

clk

но

# Ina

0

1010 X1000 X1100 X1101 X1010 X1000 X1100 X

X 1000 X 1100 X 1101 X 1010

⊕ Outa

B 1010

1010

X st1 X st2 X st3 X st0 X st1 X st2 X

X st1 X st2 X st3 X

Մ stO

st0

st0

c st

3,

```

4、

方法 1,添加辅助进程对输出数据进行锁存

方法 2,将双进程状态机改写为单进程状态机,其输出也是锁存过了,故能消除毛刺

方法 3, 使用状态位直接输出型状态机编码方式, 其输出直接由当前状态输出, 也没有毛刺

# RESEARCH CENTER FOR VLSI AND SYSTEMS 超大规模集成电路与系统研究中心